Part Number: TDA4VL-Q1

Other Parts Discussed in Thread: TDA4VL

Hello ,

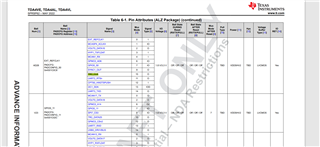

we need to configure the TRACE_CLK

1-The Register PADCONFIG_1 with address 0x4301C004 , I configured it as Output with value 10 to enable the CLK

2-The Register PADCONFIG_50 with 0x4301C0C8 , I configured it as Output with value 10 to enable the CLK

This is the right configuration or we need something else?

Also I need to know the names of ETM register need to be configured through the Isystem Debugger?