Other Parts Discussed in Thread: SYSCONFIG

Using a hard coded GPMC configuration we are noticing that the GPMC is not performing as indicated on the AM64 Datasheet/Technical Reference Manual. We are using hardcoded GPMC values due to the limitations of the the Ti driver.

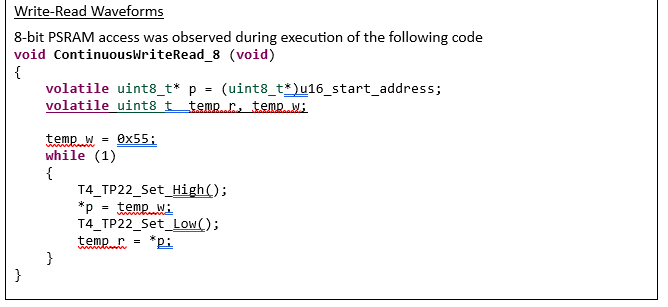

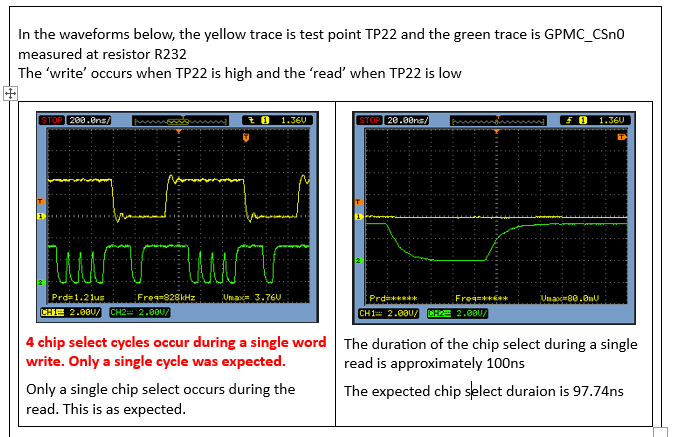

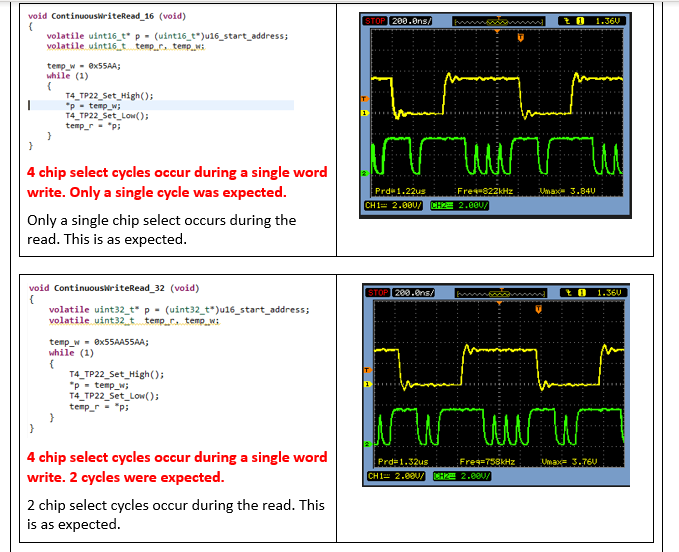

The chip select line seems to be over active on the writing.