Part Number: PROCESSOR-SDK-AM64X

Other Parts Discussed in Thread: AM2434

Hello,

I have a question regarding GPIO configurations on the AM64x/AM64243x.

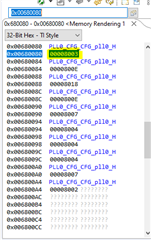

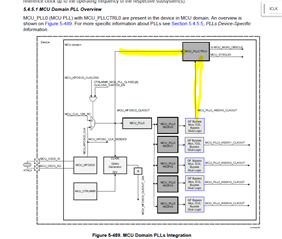

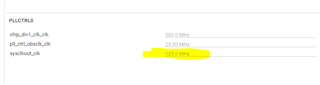

In the GPIO Programming Guide section of the reference manual (section 12.1.2.5), there is a Global Initialization sub section (12.1.2.5.1.1). The Table 12-121 describes the need to initialize tje surrounding modules before initializing any of the GPIOs. It talks about enabling the module reset and enabling the interface and functional clocks.

Can you please explain how and what registers need to be written to in order to configure those? I can't seem to find anything in the API that explains how to do this.

I inserted a picture of the table in question.

Thank you!