hi expert

sdk8.2 qnx+rtos

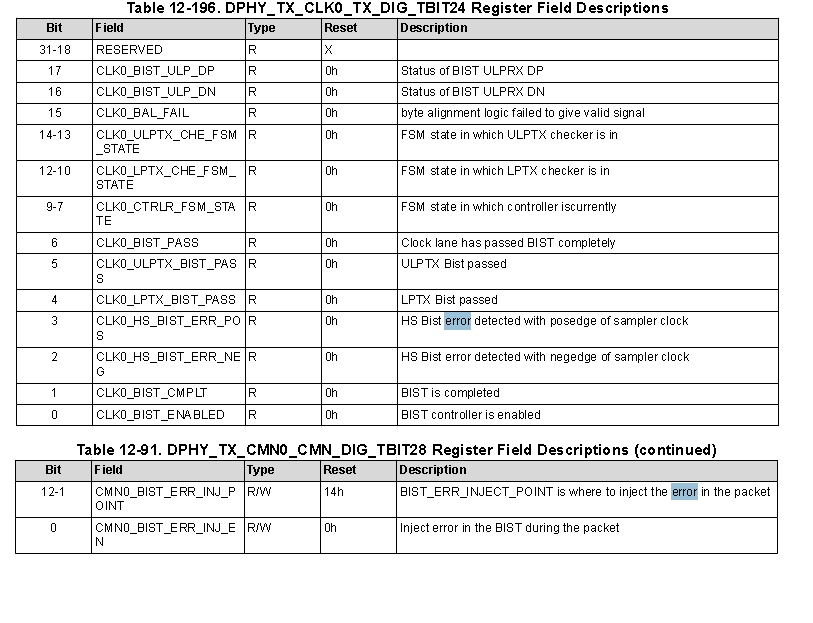

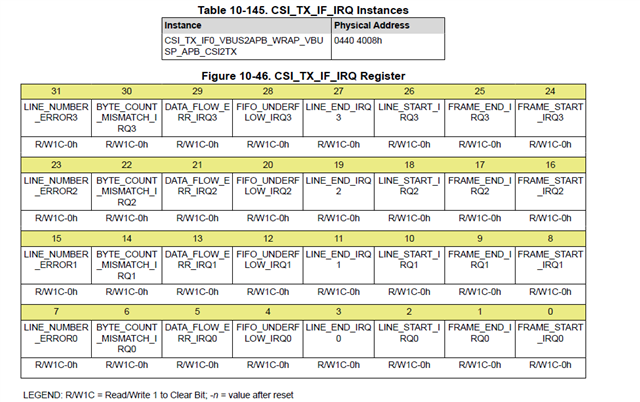

1.Is there a technical manual provided for TDA4 CSITX status and fault registers outside of the TRM manual

2.Is there a successful mass production case of TDA4 with CSITX direct connection (no Serializer and deserializer on the link), especially the successful mass production case of direct connection 8155

3.At present, the product has been mass-produced, and there are serious issues related to CSITX in the end market. We expect TI to provide a local interface person in China, who will coordinate the 8155 chip technology interface person with OEM, as well as Tire1 of TDA4 and 8155, to solve the problem together and discuss follow-up strategies