Hello TI support,

I am working with a simple demo can application to transmit a CAN frame cyclically on every 1second.

Interrupt based configuration and HW is not transmitting 1st frame which is requested to transmit.

Due to non transmission of 1st frame, consecutive frames are not getting transmitted and Can in BUSY state.

All Can_Write function requests are returned with Can Busy.

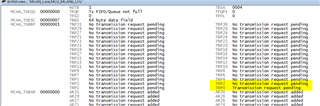

I have observed during debugging, Transmission request pending.

Could you please let me know, any pointers to debug and fix the issue.

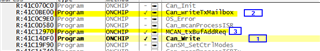

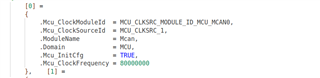

Attached Can, Dio, & Mcu configuration files.

For the CAN PORT initialization, we have taken code from mcal demo.

Kind regards,

Hari

/* This source file for CAN Port Initialaztion of TDA4 target*/

/*==================[inclusions]============================================*/

#include <Std_Types.h> /* AUTOSAR standard types */

#include <TSAutosar.h> /* EB specific standard types */

#include <Can_Port_Init.h> /* port initialization*/

void CanApp_PlatformInit()

{

uint32 regVal = 0U;

/* Unlock lock key registers for Partition 7: IO PAD

configuration registers in MAIN_CTRL_MMR */

/* write Partition 7 Lock Key 0 Register */

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1D008, 0x68EF3490);

/* write Partition 7 Lock Key 1 Register */

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1D00C, 0xD172BC5A);

/* Check for unlock */

regVal = LLD_REG32_RD(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1D008);

while ((regVal & 0x1) != 0x1U)

{

regVal = LLD_REG32_RD(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1D008);

}

/* Unlock lock key registers for Partition 7: IO PAD

configuration registers in MAIN_CTRL_MMR */

/* write Partition 7 Lock Key 0 Register */

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1D008, 0x68EF3490);

/* write Partition 7 Lock Key 1 Register */

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1D00C, 0xD172BC5A);

/* Check for unlock */

regVal = LLD_REG32_RD(CSL_CTRL_MMR0_CFG0_BASE + 0x1D008);

while ((regVal & 0x1) != 0x1U)

{

regVal = LLD_REG32_RD(CSL_CTRL_MMR0_CFG0_BASE + 0x1D008);

}

/* Unlocking done */

/* Below code will be replaced by Port module in further releases */

/* MCU MCAN 0 Tx PAD configuration */

regVal = 0x60000U;

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1C0A8U, regVal);

/* MCU MCAN 0 Rx PAD configuration */

regVal = 0x60000U;

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1C0ACU, regVal);

/* MCU MCAN 1 Tx PAD configuration */

regVal = 0x60000U;

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1C0C0U, regVal);

/* MCU MCAN 1 Rx PAD configuration */

regVal = 0x60000U;

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + 0x1C0C4U, regVal);

/* MAIN MCAN 0 Tx PAD configuration */

regVal = 0x60000U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C20CU, regVal);

/* MAIN MCAN 0 Rx PAD configuration */

regVal = 0x60000U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C208U, regVal);

/* MAIN MCAN 4 Tx PAD configuration */

regVal = 0x60006U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C020U, regVal);

/* MAIN MCAN 4 Rx PAD configuration */

regVal = 0x60006U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C024U, regVal);

/* MAIN MCAN 9 Tx PAD configuration */

regVal = 0x60006U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C0CCU, regVal);

/* MAIN MCAN 9 Rx PAD configuration */

regVal = 0x60006U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C0D0U, regVal);

/* MAIN MCAN 11 Tx PAD configuration */

regVal = 0x60006U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C11CU, regVal);

/* MAIN MCAN 11 Rx PAD configuration */

regVal = 0x60006U;

LLD_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE + 0x1C120U, regVal);

/* Take MCAN transceivers out of STB mode i.e NORMAL Mode */

CanApp_EnableTransceivers();

}

void CanApp_EnableTransceivers(void)

{

uint32 regVal = 0U;

Dio_LevelType dioPinLevel[2U];

/* Take MCAN transceiver out of STB mode for MCU MCAN0 */

/* Below code will be replaced by Port module in further releases */

/* Pin mux configuration of Dio Pin 355 */

regVal = 0x08050007U;

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + CSL_WKUP_CTRL_MMR_CFG0_PADCONFIG44, regVal);

/* Set Pin direction to output */

regVal = LLD_REG32_RD(CSL_WKUP_GPIO0_BASE + 0x10U);

regVal &= (~(1U << 0x0U));

LLD_REG32_WR(CSL_WKUP_GPIO0_BASE + 0x10U, regVal);

/* Drive Pin to High */

Dio_WriteChannel(CAN_TRCV_MCU_MCAN_0, STD_HIGH);

/* Read Pin level */

dioPinLevel[1U] = Dio_ReadChannel(CAN_TRCV_MCU_MCAN_0);

/*Read back the pin levels to ensure transceiver is enabled*/

if (STD_HIGH != dioPinLevel[1U])

{

while(1);

}

else

{

regVal = 0x08050007U;

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE +

CSL_WKUP_CTRL_MMR_CFG0_PADCONFIG38, regVal);

/* Set Pin direction to output */

regVal = LLD_REG32_RD(CSL_WKUP_GPIO0_BASE + 0x38U);

regVal &= (~(1U << 0x16U));

LLD_REG32_WR(CSL_WKUP_GPIO0_BASE + 0x38U, regVal);

/* Drive Pin to High */

Dio_WriteChannel(54U, STD_HIGH);

/* Read Pin level */

dioPinLevel[1U] = Dio_ReadChannel(54U);

/*Read back the pin levels to ensure transceiver is enabled*/

if (STD_HIGH != dioPinLevel[1U])

{

while(1);

}

}

/* Take MCAN transceiver out of STB mode for MCU MCAN1 */

/* Below code will be replaced by Port module in further releases */

/* Pin mux configuration of Dio Pin 2 */

regVal = 0x08050007U;

LLD_REG32_WR(CSL_WKUP_CTRL_MMR0_CFG0_BASE + CSL_WKUP_CTRL_MMR_CFG0_PADCONFIG46, regVal);

/* Set Pin direction to output */

regVal = LLD_REG32_RD(CSL_WKUP_GPIO0_BASE + 0x10U);

regVal &= (~(1U << 0x2U));

LLD_REG32_WR(CSL_WKUP_GPIO0_BASE + 0x10U, regVal);

/* Drive Pin to Low */

Dio_WriteChannel(CAN_TRCV_MCU_MCAN_1, STD_LOW);

/* Read Pin level */

dioPinLevel[1U] = Dio_ReadChannel(CAN_TRCV_MCU_MCAN_1);

/*Read back the pin levels to ensure transceiver is enabled*/

if (STD_LOW != dioPinLevel[1U])

{

while(1);/*

" Error in Enabling CAN Transceiver MCU MCAN1!!!\n");*/

}

return;

}

/*

*

* Copyright (C) 2023 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/*****************************************************************************

Project: simple_demo_can_rte_test

Date : 2024-05-22 20:17:00

This file is generated by EB Tresos

Do not modify this file,otherwise the software may behave in unexpected way.

******************************************************************************/

#include "Mcu.h"

#ifdef __cplusplus

extern "C" {

#endif

/* ---- Perform version checking ----------------------------------------- */

#if ((MCU_SW_MAJOR_VERSION != (9U))||(MCU_SW_MINOR_VERSION != (0U)))

#error "Version numbers of Mcu_PBcfg.c and Mcu_Cfg.h are inconsistent!"

#endif

#define MCU_START_SEC_CONFIG_DATA

#include "Mcu_MemMap.h"

/*********************************************************************************************************************

* Exported Object Declarations

*********************************************************************************************************************/

extern Std_ReturnType Mcu_CB_App_Implementation(uint32 moduleId, uint32 clkId, uint64 parentId);

#define MCU_STOP_SEC_CONFIG_DATA

#include "Mcu_MemMap.h"

#define MCU_START_SEC_CONFIG_DATA

#include "Mcu_MemMap.h"

static Mcu_ClockConfigType McuApp_McuClockConfig[] =

{

[0] =

{

.Mcu_ClockModuleId = MCU_CLKSRC_MODULE_ID_MCU_MCAN0,

.Mcu_ClockSourceId = MCU_CLKSRC_1,

.ModuleName = Mcan,

.Domain = MAIN,

.Mcu_InitCfg = TRUE,

.Mcu_ClockFrequency = 19200000

}, [1] =

{

.Mcu_ClockModuleId = MCU_CLKSRC_MODULE_ID_MCU_MCSPI0,

.Mcu_ClockSourceId = MCU_CLKSRC_0,

.ModuleName = Mcspi,

.Domain = MCU,

.Mcu_InitCfg = TRUE,

.Mcu_ClockFrequency = 25000000

}, [2] =

{

.Mcu_ClockModuleId = MCU_CLKSRC_MODULE_ID_MCU_TIMER0,

.Mcu_ClockSourceId = MCU_CLKSRC_0,

.ModuleName = Timer,

.Domain = MAIN,

.Mcu_InitCfg = TRUE,

.Mcu_ClockFrequency = 500000000

}, [3] =

{

.Mcu_ClockModuleId = MCU_CLKSRC_MODULE_ID_MAIN_ECAP0,

.Mcu_ClockSourceId = MCU_CLKSRC_0,

.ModuleName = Ecap,

.Domain = MAIN,

.Mcu_InitCfg = TRUE,

.Mcu_ClockFrequency = 24000000

}};

#define MCU_STOP_SEC_CONFIG_DATA

#include "Mcu_MemMap.h"

#define MCU_START_SEC_CONFIG_DATA

#include "Mcu_MemMap.h"

CONST(Mcu_ConfigType, MCU_CONFIG_DATA) McuModuleConfiguration =

{

.Mcu_Mode = 0,

/**< Configuration of Mcu Mode */

.Mcu_ResetMode = MCU_PERFORM_RESET_MODE_WARM,

/**< Configuration of Mcu Reset Mode */

.Mcu_ClockConfig = &McuApp_McuClockConfig[0U],

/**< Configuration of Module functional clock source */

.Mcu_NumberOfClockConfig = ARRAYSIZE(McuApp_McuClockConfig),

/**< Number of entries in Mcu_ClockConfig */

.Mcu_CBK_Function = Mcu_CB_App_Implementation,

/**< Call back Function */

};

CONST(Mcu_ResetStatusMap,

MCU_CONST) Mcu_ResetStatusMapTbl[MCU_RESET_STATUS_NUMBER] =

{

{

.rawresetval = SW_MAIN_POR,

.resetReason = MCU_POWER_ON_RESET

},

{

.rawresetval = SW_MCU_WARM_RST,

.resetReason = MCU_WATCHDOG_RESET

},

{

.rawresetval = MCU_RESETZ,

.resetReason = MCU_SW_RESET

},

{

.rawresetval = COLD_OUT_RST,

.resetReason = MCU_COLD_SW_RESET

},

{

.rawresetval = DEBUG_RST_OCCURED,

.resetReason = MCU_DEBUG_RESET

},

{

.rawresetval = MCU_RESET_UNDEFINED,

.resetReason = MCU_RESET_UNDEFINED

},

};

CONST(Mcu_ResetInfo, MCU_CONST) Mcu_ResetInfoTbl =

{

.numFields = MCU_UTILS_ARRAYSIZE(Mcu_ResetStatusMapTbl),

.resetMap = &Mcu_ResetStatusMapTbl[0]

};

#define MCU_STOP_SEC_CONFIG_DATA

#include "Mcu_MemMap.h"

/*******************************************************************************

* END OF FILE: Mcu_PBcfg.c *

******************************************************************************/

/*

*

* Copyright (c) 2023 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/*

Note: Elektrobit Automotive GmbH modified the original code provided

by the third party supplier. The modification is provided for

convenience.

Please use the modification on your discretion and account, or

use the unmodified files provided with this distribution.

Please see for the reasons in the file ImportantNotes.txt for tag

ASCTI-353 Code Compilation error for CAN driver

*/

/***************************************************************************

Project: simple_demo_can_rte_test

Date : 2024-05-17 10:17:19

This file is generated by EB Tresos

Do not modify this file, otherwise the software may behave in unexpected way.

*****************************************************************************/

/*******************************************************************************

* INCLUDES

******************************************************************************/

#include "Can.h"

#include "Can_Cfg.h"

/*

* Design: MCAL-6077,MCAL-6079,MCAL-5907

*/

/* Version checking */

#if ((CAN_SW_MAJOR_VERSION != (9U))||(CAN_SW_MINOR_VERSION != (0U)))

#error "Version numbers of Can_Cfg.c and Can.h are inconsistent!"

#endif

/*******************************************************************************

* GLOBAL DATA

******************************************************************************/

#define CAN_START_SEC_CONFIG_DATA

#include "Can_MemMap.h"

/* Controller structure defined here for all config sets */

const struct Can_ControllerStruct_PC

CanConfigSet_PC_EcuTestNode =

{

CanConf_CanController_EcuTestNode, /* Id as provided by GUI */

(boolean)TRUE, /* Contoller is used=1 or not_used=0*/

0x40500000U, /* Can Controller Base Address */

CAN_TX_RX_PROCESSING_INTERRUPT, /* Can Rx Processing Type */

CAN_TX_RX_PROCESSING_INTERRUPT, /* Can Tx Processing Type */

(boolean)TRUE,/* BusOff TRUE = Interrupt FALSE = Polling */

CAN_CONTROLLER_INSTANCE_MCU_MCAN0, /* Controller Instance */

(boolean)TRUE, /* CAN FD Mode Enable */

};

const struct Can_ControllerStruct_PC

*CanConfigSet_CanController_List_PC[CAN_NUM_CONTROLLER]=

{

&CanConfigSet_PC_EcuTestNode,

};

/* All the Mailbox objects(MB's) will be defined here for all config sets */

static const struct Can_MailboxStruct_PC

CanConfigSet_PC_HOH_2_EcuTestNode =

{

CanConf_CanHardwareObject_HOH_2_EcuTestNode, /* CanObjectId - Holds handle Id */

};

static const struct Can_MailboxStruct_PC

CanConfigSet_PC_HOH_0_EcuTestNode =

{

CanConf_CanHardwareObject_HOH_0_EcuTestNode, /* CanObjectId - Holds handle Id */

};

/* List of the Mailboxes */

const struct Can_MailboxStruct_PC

*CanConfigSet_CanHardwareObject_List_PC[CAN_NUM_MAILBOXES] =

{

&CanConfigSet_PC_HOH_2_EcuTestNode,

&CanConfigSet_PC_HOH_0_EcuTestNode,

};

extern CONST(uint32, CAN_CONST)

Can_MCANSSBaseAddr[CAN_MAX_CONTROLLER] =

{

0x40520000U, /* MCU_MCAN0_SS */

0x40560000U, /* MCU_MCAN1_SS*/

0x2700000U, /* MCAN0_SS */

0x2710000U, /* MCAN1_SS*/

0x2720000U, /* MCAN2_SS */

0x2730000U, /* MCAN3_SS */

0x2740000U, /* MCAN4_SS */

0x2750000U, /* MCAN5_SS */

0x2760000U, /* MCAN6_SS */

0x2770000U, /* MCAN7_SS */

0x2780000U, /* MCAN8_SS*/

0x2790000U, /* MCAN9_SS*/

0x27a0000U, /* MCAN10_SS */

0x27b0000U, /* MCAN11_SS */

0x27c0000U, /* MCAN12_SS*/

0x27d0000U, /* MCAN13_SS */

};

extern CONST(uint32, CAN_CONST)

Can_MCANCoreRegBaseAddr[CAN_MAX_CONTROLLER] =

{

0x40528000U, /* MCU_MCAN0_CFG */

0x40568000U, /* MCU_MCAN1_CFG*/

0x2701000U, /* MCAN0_CFG */

0x2711000U, /* MCAN1_CFG*/

0x2721000U, /* MCAN2_CFG */

0x2731000U, /* MCAN3_CFG */

0x2741000U, /* MCAN4_CFG */

0x2751000U, /* MCAN5_CFG */

0x2761000U, /* MCAN6_CFG */

0x2771000U, /* MCAN7_CFG */

0x2781000U, /* MCAN8_CFG*/

0x2791000U, /* MCAN9_CFG*/

0x27a1000U, /* MCAN10_CFG */

0x27b1000U, /* MCAN11_CFG */

0x27c1000U, /* MCAN12_CFG*/

0x27d1000U, /* MCAN13_CFG */

};

extern CONST(uint32, CAN_CONST)

Can_MCANECCAggrRegBaseAddr[CAN_MAX_CONTROLLER] =

{

0x40700000U, /* MCU_MCAN0_ECC_AGGR */

0x40701000U, /* MCU_MCAN1_ECC_AGGR*/

0x2A78000U, /* MCAN0_ECC_AGGR */

0x2A79000U, /* MCAN1_ECC_AGGR */

0x2A7A000U, /* MCAN2_ECC_AGGR*/

0x2A7B000U, /* MCAN3_ECC_AGGR */

0x2A7C000U, /* MCAN4_ECC_AGGR */

0x2A7D000U, /* MCAN5_ECC_AGGR */

0x2A7E000U, /* MCAN6_ECC_AGGR */

0x2A7F000U, /* MCAN7_ECC_AGGR */

0x2A40000U, /* MCAN8_ECC_AGGR */

0x2A41000U, /* MCAN9_ECC_AGGR*/

0x2A42000U, /* MCAN10_ECC_AGGR*/

0x2A43000U, /* MCAN11_ECC_AGGR */

0x2A44000U, /* MCAN12_ECC_AGGR */

0x2A45000U, /* MCAN13_ECC_AGGR*/

};

#define CAN_STOP_SEC_CONFIG_DATA

#include "Can_MemMap.h"

/* ========================================================================== */

/* Function Definitions */

/* ========================================================================== */

/*******************************************************************************

* End of File: Can_Cfg.c

******************************************************************************/

/*

*

* Copyright (c) 2023 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/*

Note: Elektrobit Automotive GmbH modified the original code provided

by the third party supplier. The modification is provided for

convenience.

Please use the modification on your discretion and account, or

use the unmodified files provided with this distribution.

Please see for the reasons in the file ImportantNotes.txt for tag

ASCTI-353 Code Compilation error for CAN driver

*/

/*

* Design: MCAL-5949

*/

/***************************************************************************

Project: simple_demo_can_rte_test

Date : 2024-05-17 10:17:19

This file is generated by EB Tresos

Do not modify this file, otherwise the software may behave in unexpected way.

*****************************************************************************/

/*******************************************************************************

* INCLUDES

******************************************************************************/

#include "Can.h"

#include "Can_Cfg.h"

/* Version checking */

#if ((CAN_SW_MAJOR_VERSION != (9U))||(CAN_SW_MINOR_VERSION != (0U)))

#error "Version numbers of Can_PBcfg.c and Can.h are inconsistent!"

#endif

/*******************************************************************************

* GLOBAL DATA

******************************************************************************/

#define CAN_START_SEC_CONFIG_DATA

#include "Can_MemMap.h"

/* Baud Rate Structure for all configsets */

static Can_BaudConfigType

CanConfigSet_EcuTestNode_CanControllerBaudrateConfig =

{

500U, /* in Kbps */

1U, /* Prop Segement value */

7U, /* Phase Segment 1 */

7U, /* Phase Segment 2 */

4U, /* Sync jump width */

19U, /* Sum of all timing parameters */

10U, /* Controller BRP value for Baud */

/* Data phase Baudrate */

{

2000U, /* in Kbps */

0U, /* Prop Segement value */

1U, /* Phase Segment 1 */

2U, /* Phase Segment 2 */

1U, /* Sync jump width */

4U, /* Sum of all timing parameters */

10U, /* Controller BRP value for Baud */

180U, /* Specifies the Transceiver Delay Compensation Offset in ns */

(boolean)TRUE, /* Specifies if the bit rate switching shall be used */

}

};

/*List of the Baudrate structures */

static Can_BaudConfigType

*CanConfigSet_EcuTestNode_BaudRateConfigList[]=

{

&CanConfigSet_EcuTestNode_CanControllerBaudrateConfig,

};

/* Controller structure defined here for all config sets */

static Can_ControllerType

CanConfigSet_EcuTestNode =

{

&CanConfigSet_EcuTestNode_CanControllerBaudrateConfig, /* pointer to default Baud structure */

CanConfigSet_EcuTestNode_BaudRateConfigList, /* List of available Baudrate structs */

};

/*List of the Controller structures */

static Can_ControllerType

*CanConfigSet_CanController_List[]=

{

&CanConfigSet_EcuTestNode,

};

/* HW Filter structure for all configsets */

static Can_HwFilterType

CanConfigSet_HOH_2_EcuTestNode_CanHwFilter =

{

256U, /*CanHwFilterCode*/

2047U, /*Filter Mask*/

};

/*List of the HW Filter structures */

static Can_HwFilterType

*CanConfigSet_HOH_2_EcuTestNode_HwFilterConfigList[]=

{

&CanConfigSet_HOH_2_EcuTestNode_CanHwFilter,

};

/* All the Mailbox objects(MB's) will be defined here for all config sets */

static Can_MailboxType

CanConfigSet_HOH_2_EcuTestNode =

{

0U, /* CanHandleType 0=Full, 1=Basic */

0U, /* CanIdType 0=standard 1=Extended 2=Mixed*/

0U, /* HwHandle i.e Mailbox - Hw object in the controller */

1U, /* Length of the Mailbox */

CAN_MAILBOX_DIRECTION_RX, /* CanObjectType - Direction of Mailbox*/

&CanConfigSet_PC_EcuTestNode, /* Controller */

CanConfigSet_HOH_2_EcuTestNode_HwFilterConfigList, /* List of HW Filter structs */

1U, /* Hw Filter Count */

0U, /* Padding value for CAN FD message */

(boolean)FALSE, /* CanHardwareObjectUsesPolling */

};

static Can_MailboxType

CanConfigSet_HOH_0_EcuTestNode =

{

0U, /* CanHandleType 0=Full, 1=Basic */

0U, /* CanIdType 0=standard 1=Extended 2=Mixed*/

0U, /* HwHandle i.e Mailbox - Hw object in the controller */

1U, /* Length of the Mailbox */

CAN_MAILBOX_DIRECTION_TX, /* CanObjectType - Direction of Mailbox*/

&CanConfigSet_PC_EcuTestNode, /* Controller */

NULL_PTR, /* List of HW Filter structs */

0U, /* Hw Filter Count */

0U, /* Padding value for CAN FD message */

(boolean)FALSE, /* CanHardwareObjectUsesPolling */

};

/* List of the Mailboxes */

static Can_MailboxType

*CanConfigSet_CanHardwareObject_List[] =

{

&CanConfigSet_HOH_2_EcuTestNode,

&CanConfigSet_HOH_0_EcuTestNode,

};

extern CONST(uint32, CAN_CONST)

Can_MsgmemRAMBaseAddr[CAN_MAX_CONTROLLER] =

{

0x40500000U, /* MCU MCAN0 */

0x40540000U, /* MCU MCAN1 */

0x2708000U, /* Main MCAN0 */

0x2718000U, /* Main MCAN1 */

0x2728000U, /* Main MCAN2 */

0x2738000U, /* Main MCAN3 */

0x2748000U, /* Main MCAN4 */

0x2758000U, /* Main MCAN5 */

0x2768000U, /* Main MCAN6 */

0x2778000U, /* Main MCAN7 */

0x2788000U, /* Main MCAN8 */

0x2798000U, /* Main MCAN9 */

0x27a8000U, /* Main MCAN10 */

0x27b8000U, /* Main MCAN11 */

0x27c8000U, /* Main MCAN12 */

0x27d8000U, /* Main MCAN13 */

};

#define CAN_STOP_SEC_CONFIG_DATA

#include "Can_MemMap.h"

/* ========================================================================== */

/* Function Definitions */

/* ========================================================================== */

#define CAN_START_SEC_ISR_CODE

#include "Can_MemMap.h"

ISR(Can_0_Int0ISR)

{

Can_IntISR_Function(CAN_CONTROLLER_INSTANCE_MCU_MCAN0, 0x40500000U);

}

#define CAN_STOP_SEC_ISR_CODE

#include "Can_MemMap.h"

#define CAN_START_SEC_CONFIG_DATA

#include "Can_MemMap.h"

/*Can Config struct */

const struct Can_ConfigType_s CanConfigSet =

{

CanConfigSet_CanController_List, /* Controller List Pointer */

(1U), /* max Controllers */

CanConfigSet_CanHardwareObject_List, /* Mailbox List Pointer */

(2U),/* total number of mail boxes in this configset */

.MaxBaudConfigID =

{

[0] = 0U

}, /* Baud rate structure id */

NULL_PTR, /* Reserved Param used for future use */

};

#define CAN_STOP_SEC_CONFIG_DATA

#include "Can_MemMap.h"

/*******************************************************************************

* End of File: Can_PBcfg.c

******************************************************************************/

/*

*

* Copyright (c) 2023 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/***********************************************************************

Project: simple_demo_can_rte_test

Date : 2024-05-17 10:17:19

This file is generated by EB Tresos

Do not modify this file, otherwise the software may behave in

unexpected way.

***********************************************************************/

/**

* \file Dio_Cfg.c

*

* \brief This file contains generated pre compile time configuration file

* for DIO MCAL driver

*

*/

/* ========================================================================== */

/* Include Files */

/* ========================================================================== */

#include "Std_Types.h"

#include "Dio.h"

#include "Dio_Cfg.h"

/* ========================================================================== */

/* Version Check */

/* ========================================================================== */

#if ((DIO_SW_MAJOR_VERSION != (9U))||(DIO_SW_MINOR_VERSION != (0U)))

#error "Version numbers of Dio_Cfg.c and Dio.h are inconsistent!"

#endif

/* ========================================================================== */

/* Global Variables */

/* ========================================================================== */

#ifdef __cplusplus

extern "C" {

#endif

#define DIO_START_SEC_CONFIG_DATA

#include "Dio_MemMap.h"

/* generation of runtime configuration */

/*<DIO_GROUP_LIST>*/

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_DioPort_0_ChannelGroup[0] =

{

};

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_WKUP_GPIO0_B01_ChannelGroup[1] =

{

[0] =

{

.port = 0U,

.mask = 0x00000003U,

.offset = 0U,

},

};

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_WKUP_GPIO0_B23_ChannelGroup[0] =

{

};

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_GPIO0_B01_ChannelGroup[0] =

{

};

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_GPIO0_B23_ChannelGroup[0] =

{

};

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_GPIO0_B45_ChannelGroup[0] =

{

};

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_GPIO1_B01_ChannelGroup[0] =

{

};

CONST(Dio_ChannelGroupType, DIO_CONST)

DioConfig_GPIO1_B23_ChannelGroup[0] =

{

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_DioPort_0_ChannelGroupRef[0] =

{

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_WKUP_GPIO0_B01_ChannelGroupRef[1] =

{

[0] = &DioConfig_WKUP_GPIO0_B01_ChannelGroup[0],

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_WKUP_GPIO0_B23_ChannelGroupRef[0] =

{

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_GPIO0_B01_ChannelGroupRef[0] =

{

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_GPIO0_B23_ChannelGroupRef[0] =

{

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_GPIO0_B45_ChannelGroupRef[0] =

{

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_GPIO1_B01_ChannelGroupRef[0] =

{

};

P2CONST(void,AUTOMATIC, DIO_CONST)

DioConfig_GPIO1_B23_ChannelGroupRef[0] =

{

};

#if (STD_ON == DIO_DEV_ERROR_DETECT)

/* Valid mask is always generated for all the ports. The module will use this

to check if a port & channel combination is enabled, reserved pins check is

also performed, Reserved pins are platform dependent, please refer to TRM*/

CONST (uint32,DIO_CONST)

Dio_ConfigValidChannelMask[30U] =

{

[DioConf_DioPort_DioPort_0] = (0U \

| ((uint32)1U << 0U) \

),

[DioConf_DioPort_WKUP_GPIO0_B01] = (0U \

| ((uint32)1U << 0U) \

| ((uint32)1U << 1U) \

| ((uint32)1U << 2U) \

| ((uint32)1U << 3U) \

| ((uint32)1U << 4U) \

| ((uint32)1U << 5U) \

| ((uint32)1U << 6U) \

| ((uint32)1U << 7U) \

| ((uint32)1U << 8U) \

| ((uint32)1U << 9U) \

| ((uint32)1U << 10U) \

| ((uint32)1U << 11U) \

| ((uint32)1U << 12U) \

| ((uint32)1U << 13U) \

| ((uint32)1U << 14U) \

| ((uint32)1U << 15U) \

| ((uint32)1U << 16U) \

| ((uint32)1U << 17U) \

| ((uint32)1U << 18U) \

| ((uint32)1U << 19U) \

| ((uint32)1U << 20U) \

| ((uint32)1U << 21U) \

| ((uint32)1U << 22U) \

| ((uint32)1U << 23U) \

| ((uint32)1U << 24U) \

| ((uint32)1U << 25U) \

| ((uint32)1U << 26U) \

| ((uint32)1U << 27U) \

| ((uint32)1U << 28U) \

| ((uint32)1U << 29U) \

| ((uint32)1U << 30U) \

| ((uint32)1U << 31U) \

),

[DioConf_DioPort_WKUP_GPIO0_B23] = (0U \

| ((uint32)1U << 0U) \

| ((uint32)1U << 1U) \

| ((uint32)1U << 2U) \

| ((uint32)1U << 3U) \

| ((uint32)1U << 4U) \

| ((uint32)1U << 5U) \

| ((uint32)1U << 6U) \

| ((uint32)1U << 7U) \

| ((uint32)1U << 8U) \

| ((uint32)1U << 9U) \

| ((uint32)1U << 10U) \

| ((uint32)1U << 11U) \

| ((uint32)1U << 12U) \

| ((uint32)1U << 13U) \

| ((uint32)1U << 14U) \

| ((uint32)1U << 15U) \

| ((uint32)1U << 16U) \

| ((uint32)1U << 17U) \

| ((uint32)1U << 18U) \

| ((uint32)1U << 19U) \

| ((uint32)1U << 20U) \

| ((uint32)1U << 21U) \

| ((uint32)1U << 22U) \

| ((uint32)1U << 23U) \

),

[2] = (0U),

[3] = (0U),

[4] = (0U),

[5] = (0U),

[DioConf_DioPort_GPIO0_B01] = (0U \

| ((uint32)1U << 0U) \

| ((uint32)1U << 1U) \

| ((uint32)1U << 2U) \

| ((uint32)1U << 3U) \

| ((uint32)1U << 4U) \

| ((uint32)1U << 5U) \

| ((uint32)1U << 6U) \

| ((uint32)1U << 7U) \

| ((uint32)1U << 8U) \

| ((uint32)1U << 9U) \

| ((uint32)1U << 10U) \

| ((uint32)1U << 11U) \

| ((uint32)1U << 12U) \

| ((uint32)1U << 13U) \

| ((uint32)1U << 14U) \

| ((uint32)1U << 15U) \

| ((uint32)1U << 16U) \

| ((uint32)1U << 17U) \

| ((uint32)1U << 18U) \

| ((uint32)1U << 19U) \

| ((uint32)1U << 20U) \

| ((uint32)1U << 21U) \

| ((uint32)1U << 22U) \

| ((uint32)1U << 23U) \

| ((uint32)1U << 24U) \

| ((uint32)1U << 25U) \

| ((uint32)1U << 26U) \

| ((uint32)1U << 27U) \

| ((uint32)1U << 28U) \

| ((uint32)1U << 29U) \

| ((uint32)1U << 30U) \

| ((uint32)1U << 31U) \

),

[DioConf_DioPort_GPIO0_B23] = (0U \

| ((uint32)1U << 0U) \

| ((uint32)1U << 1U) \

| ((uint32)1U << 2U) \

| ((uint32)1U << 3U) \

| ((uint32)1U << 4U) \

| ((uint32)1U << 5U) \

| ((uint32)1U << 6U) \

| ((uint32)1U << 7U) \

| ((uint32)1U << 8U) \

| ((uint32)1U << 9U) \

| ((uint32)1U << 10U) \

| ((uint32)1U << 11U) \

| ((uint32)1U << 12U) \

| ((uint32)1U << 13U) \

| ((uint32)1U << 14U) \

| ((uint32)1U << 15U) \

| ((uint32)1U << 16U) \

| ((uint32)1U << 17U) \

| ((uint32)1U << 18U) \

| ((uint32)1U << 19U) \

| ((uint32)1U << 20U) \

| ((uint32)1U << 21U) \

| ((uint32)1U << 22U) \

| ((uint32)1U << 23U) \

| ((uint32)1U << 24U) \

| ((uint32)1U << 25U) \

| ((uint32)1U << 26U) \

| ((uint32)1U << 27U) \

| ((uint32)1U << 28U) \

| ((uint32)1U << 29U) \

| ((uint32)1U << 30U) \

| ((uint32)1U << 31U) \

),

[DioConf_DioPort_GPIO0_B45] = (0U \

| ((uint32)1U << 0U) \

| ((uint32)1U << 1U) \

| ((uint32)1U << 2U) \

| ((uint32)1U << 3U) \

| ((uint32)1U << 4U) \

| ((uint32)1U << 5U) \

| ((uint32)1U << 6U) \

| ((uint32)1U << 7U) \

| ((uint32)1U << 8U) \

| ((uint32)1U << 9U) \

| ((uint32)1U << 10U) \

| ((uint32)1U << 11U) \

| ((uint32)1U << 12U) \

| ((uint32)1U << 13U) \

| ((uint32)1U << 14U) \

| ((uint32)1U << 15U) \

| ((uint32)1U << 16U) \

| ((uint32)1U << 17U) \

| ((uint32)1U << 18U) \

| ((uint32)1U << 19U) \

| ((uint32)1U << 20U) \

| ((uint32)1U << 21U) \

| ((uint32)1U << 22U) \

| ((uint32)1U << 23U) \

| ((uint32)1U << 24U) \

| ((uint32)1U << 25U) \

| ((uint32)1U << 26U) \

| ((uint32)1U << 27U) \

| ((uint32)1U << 28U) \

| ((uint32)1U << 29U) \

| ((uint32)1U << 30U) \

| ((uint32)1U << 31U) \

),

[9] = (0U),

[DioConf_DioPort_GPIO1_B01] = (0U \

| ((uint32)1U << 0U) \

| ((uint32)1U << 1U) \

| ((uint32)1U << 2U) \

| ((uint32)1U << 3U) \

| ((uint32)1U << 4U) \

| ((uint32)1U << 5U) \

| ((uint32)1U << 6U) \

| ((uint32)1U << 7U) \

| ((uint32)1U << 8U) \

| ((uint32)1U << 9U) \

| ((uint32)1U << 10U) \

| ((uint32)1U << 11U) \

| ((uint32)1U << 12U) \

| ((uint32)1U << 13U) \

| ((uint32)1U << 14U) \

| ((uint32)1U << 15U) \

| ((uint32)1U << 16U) \

| ((uint32)1U << 17U) \

| ((uint32)1U << 18U) \

| ((uint32)1U << 19U) \

| ((uint32)1U << 20U) \

| ((uint32)1U << 21U) \

| ((uint32)1U << 22U) \

| ((uint32)1U << 23U) \

| ((uint32)1U << 24U) \

| ((uint32)1U << 25U) \

| ((uint32)1U << 26U) \

| ((uint32)1U << 27U) \

| ((uint32)1U << 28U) \

| ((uint32)1U << 29U) \

| ((uint32)1U << 30U) \

| ((uint32)1U << 31U) \

),

[DioConf_DioPort_GPIO1_B23] = (0U \

| ((uint32)1U << 0U) \

| ((uint32)1U << 1U) \

| ((uint32)1U << 2U) \

| ((uint32)1U << 3U) \

),

[12] = (0U),

[13] = (0U),

[14] = (0U),

[15] = (0U),

[16] = (0U),

[17] = (0U),

[18] = (0U),

[19] = (0U),

[20] = (0U),

[21] = (0U),

[22] = (0U),

[23] = (0U),

[24] = (0U),

[25] = (0U),

[26] = (0U),

[27] = (0U),

[28] = (0U),

[29] = (0U),

};

#endif /* (STD_ON == DIO_DEV_ERROR_DETECT) */

/*</DIO_GROUP_LIST>*/

#define DIO_STOP_SEC_CONFIG_DATA

#include "Dio_MemMap.h"

#define DIO_START_SEC_CONST_32

#include "Dio_MemMap.h"

const uint32 Dio_PortIdInstance[DIO_HW_UNIT_CNT + 1U] =

{

(uint32)0U,

(uint32)DIO_MAX_PORT_ID_INSTANCE_0,

(uint32)DIO_MAX_PORT_ID_INSTANCE_1,

(uint32)DIO_MAX_PORT_ID_INSTANCE_2,

(uint32)DIO_MAX_PORT_ID_INSTANCE_3,

(uint32)DIO_MAX_PORT_ID_INSTANCE_4,

(uint32)DIO_MAX_PORT_ID_INSTANCE_5,

(uint32)DIO_MAX_PORT_ID_INSTANCE_6,

(uint32)DIO_MAX_PORT_ID_INSTANCE_7,

(uint32)DIO_MAX_PORT_ID_INSTANCE_8,

(uint32)DIO_MAX_PORT_ID_INSTANCE_9,

};

const uint32 Dio_Instance[DIO_HW_UNIT_CNT] =

{

(uint32)DIO_INSTANCE_0,

(uint32)DIO_INSTANCE_1,

(uint32)DIO_INSTANCE_2,

(uint32)DIO_INSTANCE_3,

(uint32)DIO_INSTANCE_4,

(uint32)DIO_INSTANCE_5,

(uint32)DIO_INSTANCE_6,

(uint32)DIO_INSTANCE_7,

(uint32)DIO_INSTANCE_8,

(uint32)DIO_INSTANCE_9,

};

CONST(uint32, DIO_CONST)

Dio_GPIOBaseAddr[DIO_HW_UNIT_CNT] =

{

(uint32)0x42110000UL,

(uint32)0x42100000UL,

(uint32)0x600000UL,

(uint32)0x601000UL,

(uint32)0x610000UL,

(uint32)0x611000UL,

(uint32)0x620000UL,

(uint32)0x621000UL,

(uint32)0x630000UL,

(uint32)0x631000UL,

};

#define DIO_STOP_SEC_CONST_32

#include "Dio_MemMap.h"

#define DIO_START_SEC_CONST_UNSPECIFIED

#include "Dio_MemMap.h"

/*The reserved pins are taken from Platform Specific TRM*/

static CONST(DioReservedPinListType, DIO_CONST) Dio_ReservedPinList[DIO_HW_UNIT_CNT] =

{

[0] =

{

.regNum = 0U,

.numPins = 60U,

.reservedPinStart = 84U

},

[1] =

{

.regNum = 1U,

.numPins = 60U,

.reservedPinStart = 204U

},

[2] =

{

.regNum = 2U,

.numPins = 16U,

.reservedPinStart = 416U

},

[3] =

{

.regNum = 3U,

.numPins = 108U,

.reservedPinStart = 468U

},

[4] =

{

.regNum = 4U,

.numPins = 16U,

.reservedPinStart = 704U

},

[5] =

{

.regNum = 5U,

.numPins = 108U,

.reservedPinStart = 756U

},

[6] =

{

.regNum = 6U,

.numPins = 16U,

.reservedPinStart = 992U

},

[7] =

{

.regNum = 7U,

.numPins = 108U,

.reservedPinStart = 1044U

},

[8] =

{

.regNum = 8U,

.numPins = 16U,

.reservedPinStart = 1280U

},

[9] =

{

.regNum = 9U,

.numPins = 108U,

.reservedPinStart = 1332U

},

};

#define DIO_STOP_SEC_CONST_UNSPECIFIED

#include "Dio_MemMap.h"

#define DIO_START_SEC_CODE

#include "Dio_MemMap.h"

boolean Dio_isReservedPin(uint8 regNum, uint32 pinNum)

{

boolean isReservedPin = (boolean) FALSE;

uint8 i;

for (i = 0U; i < (uint8) DIO_UTILS_ARRAYSIZE(Dio_ReservedPinList); i++)

{

if (Dio_ReservedPinList[i].regNum == regNum)

{

if (Dio_ReservedPinList[i].reservedPinStart <= pinNum)

{

isReservedPin = (boolean) TRUE;

break;

}

else

{

/*Do Nothing*/

}

}

else

{

/*Do Nothing*/

}

}

if (i == (uint8) DIO_UTILS_ARRAYSIZE(Dio_ReservedPinList))

{

isReservedPin = (boolean) FALSE;

}

else

{

/*Do Nothing*/

}

return isReservedPin;

}

#define DIO_STOP_SEC_CODE

#include "Dio_MemMap.h"

#ifdef __cplusplus

}

#endif

/*******************************************************************************

* END OF FILE: DIO_LCFG.C

******************************************************************************/

/*

*

* Copyright (c) 2023 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/**

* \file Mcu_Cfg.c

*

* \brief This file contains generated pre-compile configuration file

* for MCU MCAL driver

*

*/

/*****************************************************************************

Project: simple_demo_can_rte_test

Date : 2024-05-22 20:17:00

This file is generated by EB Tresos

Do not modify this file,otherwise the software may behave in unexpected way.

******************************************************************************/

/*******************************************************************************

* END OF FILE: Mcu_Cfg.c *

******************************************************************************/