1.ti-processor-sdk-linux-adas-j784s4-evm-09_02_00_05 this is the SDK verison I used

2.the CPU is TDA4VH-Q1

How to enable DDR in line ecc?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

1.ti-processor-sdk-linux-adas-j784s4-evm-09_02_00_05 this is the SDK verison I used

2.the CPU is TDA4VH-Q1

How to enable DDR in line ecc?

Hi,

Please use the patches shared in the above link.

Best Regards,

Keerthy

when I use AM69-ECC_Fix patch

The boot has stopped at this place below

U-Boot SPL 2023.04 (May 24 2024 - 10:11:16 +0800)

EEPROM not available at 0x50, trying to read at 0x51

Reading on-board EEPROM at 0x51 failed -121

SYSFW ABI: 3.1 (firmware rev 0x0009 '9.2.4--v09.02.04 (Kool Koala)')

ECC is enabled, priming DDR which will take several seconds.

ECC: priming DDR completed in 2229 msec

SPL initial stack usage: 13456 bytes

Trying to boot from MMC2

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

------->inline ecc

---enable---->inline ecc

but when I disable CONFIG_K3_INLINE_ECC ; The system can run ;

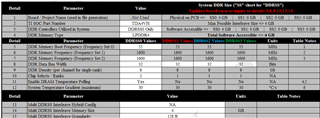

I use the 4GB lpddr4 ;

64mb x 32DQ x 8banks x 2channels

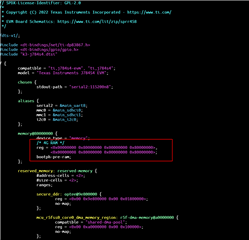

I modify k3-j784s4-evm.dts like below.

Hi Fang,

The patch is for TDA4VH-EVM which has 32 GB. For 4GB you will need to make some custom changes.

- Keerthy

Hi Fang,

There are 4 DDR controllers each catering to 8GB of DDR. How is your mapping? Is it one DDR controller which caters to all 4 GB or each DDR controller has 1GB part?

Few more points:

- Keerthy

hi Keerthy J

This is the DDR mapping.

but when I disable CONFIG_K3_INLINE_ECC ; The system can run

wen I enable CONFIG_K3_INLINE_ECC ,The uboot was stoped.

U-Boot SPL 2023.04 (May 24 2024 - 10:11:16 +0800)

EEPROM not available at 0x50, trying to read at 0x51

Reading on-board EEPROM at 0x51 failed -121

SYSFW ABI: 3.1 (firmware rev 0x0009 '9.2.4--v09.02.04 (Kool Koala)')

ECC is enabled, priming DDR which will take several seconds.

ECC: priming DDR completed in 2229 msec

SPL initial stack usage: 13456 bytes

Trying to boot from MMC2

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

------->inline ecc

---enable---->inline ecc

U-Boot SPL 2023.04 (Jun 01 2024 - 19:01:22 +0800)

EEPROM not available at 0x50, trying to read at 0x51

Reading on-board EEPROM at 0x51 failed -121

SYSFW ABI: 3.1 (firmware rev 0x0009 '9.2.4--v09.02.04 (Kool Koala)')

ECC is enabled, priming DDR which will take several seconds.

ECC: priming DDR completed in 2229 msec

SPL initial stack usage: 13456 bytes

Trying to boot from MMC2

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Timeout during frequency handshake

### ERROR ### Please RESET the board ###

Hi Fang,

DDR is not initialized correctly. Was this working without inline ECC?

- Keerthy

Hi Fang,

Keerthy mentioned that DDR did not appear to be initialized correctly because the line below in the log file is indicative of a DDR training failure. ECC should not have any impact on the training.

Timeout during frequency handshake

Are you able to provide a "diff" of the ECC disabled source (working) vs. ECC enabled (not working)?

when disable CONFIG_K3_INLINE_ECC ,the uboot can run and system can run

Thanks,

Kevin

Also, can you please comment on how repeatable results are?

Does it fail 100% of the time when you have ECC enabled?

Does it pass 100% of the time when you have ECC disabled?

How many boot attempts are made for each condition?

Thanks,

Kevin