Part Number: TDA4VH-Q1

Other Parts Discussed in Thread: MATHLIB, TDA4VH

Tool/software:

Hi,

Platform:J784s4-evm C71x(1 GHz)

SDK:ti-processor-sdk-rtos-j784s4-evm-09_02_00_05

There are several issues related to DSP C71 running memory. We now want to use the C71 to run some algorithms to reduce the operational burden of the A72 core(HLOS:Linux j784s4-evm 6.1.46).I found that the C71 program takes different time to link to different addresses(L2 Memory 512K / MSMC Sram 8M / DDR ).

1、Where do the dsplib and mathlib test cases in the SDK you provide link to run? Whether the boot mode(No Boot Mode / SD Boot Mode) has any effect.

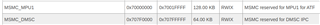

2、I found our program to run faster on L2 Memory and MSMC Sram,Due to size limitations we are going to link the program to the MSMC Sram.What makes us a little confused now is the address range of the MSMC Sram. We are currently using 0x70000000-0x70800000.You can also run the cat /proc/iomem command to verify(70000000-706effff : 70000000.sram sram@70000000). But I saw this definition in some link.cmd file in the RTOS SDK:

MSMCSRAM (RWX) : org = 0x68000000, len = 0x300000 (ti-processor-sdk-rtos-j784s4-evm-09_02_00_05\dsplib_09_02_00_04\cmake\linkers\C7120\lnk.cmd)

MSMC_C7x_1 ( RWIX ) : ORIGIN = 0x68000000 , LENGTH = 0x00300000 (ti-processor-sdk-rtos-j784s4-evm-09_02_00_05\vision_apps\platform\j784s4\rtos\c7x_1\j784s4_linker_freertos.cmd)

So what does the 0x680000000-0x68800000 address range mean?

3、We're going to run bare metal without RTOS.Do we need to do memory mapping?

4、If we need to use Mmu_map for memory mapping, I have some confusion about the value of the attrs.attrIndx attribute.I've seen several examples where the addresses 0x00000000U, 0x20000000U, 0x40000000U, and 0x60000000U are configured as Mmu_AttrIndx_MAIR0(such as c7x_mmu.c). But these addresses don't seem to be used in the program.So I want to know what's the intention here.

5、I know that the address attributes are consistent (non-cached) when configured as Mmu_AttrIndx_MAIR4.Even though I read the C71x DSP Corepac Technical Reference Manual, I don't know what is the use of Mmu_AttrIndx_MAIR7 and Mmu_AttrIndx_MAIR0.

6、I know that the address attributes are consistent (non-cached) when configured as Mmu_AttrIndx_MAIR4.In this way, ARM and DSP can get the same data directly from the same address. When I use MSMC Sram, DSP side needs to be synchronized(Call Cache_setL1DWBINV(1) function), otherwise ARM side can not read the correct data. However, frequent calls to the Cache_setL1DWBINV(1) function add time. Can I configure the MSMC Sram to the Mmu_AttrIndx_MAIR4 attribute, will this cause it not to use the Cache and make the program slower. So is there a good way to make the MSMC Sram cache-coherent?

Thanks,