Part Number: TDA4VH-Q1

Other Parts Discussed in Thread: TDA4VM

Tool/software:

Hi Ti,

Regarding the issue of a Bus error occurring after mapping PCIe BAR to process space and accessing it, there has been new progress.

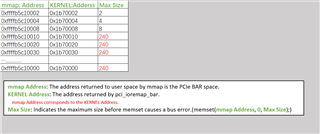

Using gdb debugging, it was found that every time the assembly instruction “str q0, [x1]” is executed, a Bus error occurs, where x1 = 0xfffff7f90028. The address after the process mmap PCIe BAR is 0xfffff7f90000. This address appears to be eight-byte aligned. I am not sure why this assembly instruction causes a Bus error. Moreover, I have checked that the address range 0xfffff7f90000-0xfffff7fA0000 has rw-s permissions before executing this instruction.

What is even more puzzling is that when running with valgrind, no Bus error occurs, and the execution completes normally without any errors in the result check. I wonder if this issue is related to PCIe. Could experts from TI help analyze this?

Regards,

Qiang