Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

With our custom board:

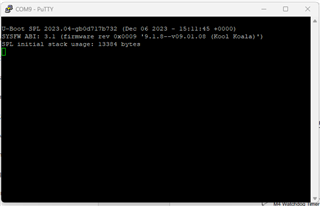

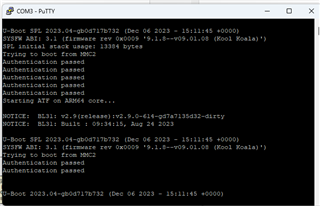

With the development board:

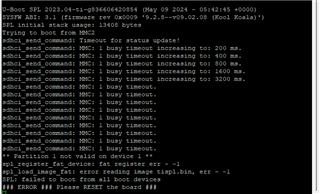

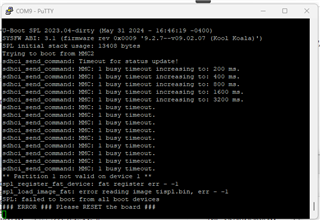

I've noticed that the SD clock seems to stop after the characters (in the first image) are displayed in the terminal window on the custom board. How far in the boot process should the SD card boot be able to proceed to. I'm starting off with "tisdk-default-image-am62xx-lp-evm.wic.xz" and hope to disable some of the configuration to use it on our custom board.