Other Parts Discussed in Thread: TDA4VH

Tool/software:

Hi all:

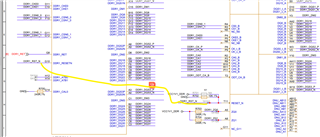

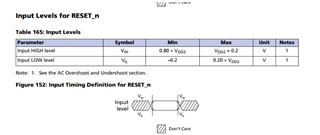

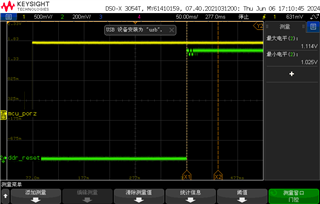

In the TDA4VH power-on timing test, we found that the Reset pin waveform of DDR was as follows, with 20mv fluctuation. This voltage was within the high level threshold of the Reset pin of DDR, and the jitter disappeared after the Cold Reset of TDA4VH turned to high level.We tested at TP702 point, and this was true for all four DDR waveforms.DDR model: MT53E2G32D4DE-046 AAT:CD

Please help to confirm the cause of this problem. I think this change has no impact on the start-up of TDA4 before the Cold Reset, but we need TI's confirmation.