Other Parts Discussed in Thread: TDA4VH, TDA4VM

Tool/software:

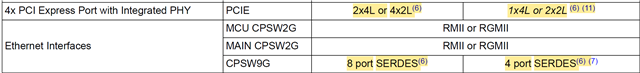

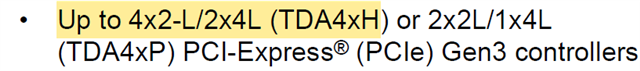

#1. Can TDA4VH PCIe work in 1 Lane mode? If Yes, can it support up to 4 x1Lane?

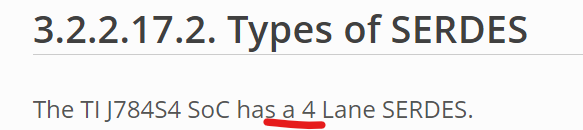

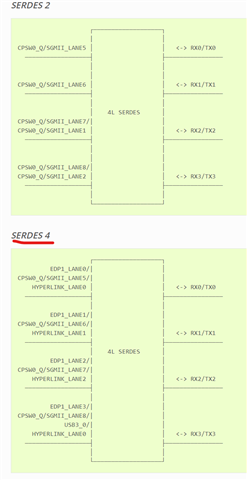

#2. If #1 yes, Is there limitation on Serdes assignment between each PCIe instance?

#3. On the EVM, QSGMII extension board used Serdes 5 and 7 for ENET-EXP-1, Serdes 6 and 8 for ENET-EXP-2, can it be any 2 pair of Serdes for one QSGMII, for example Serdes 5 and 6 for ENET-EXP-1, Serdes 7 and 8 for ENET-EXP-2?

#4, Besides the 2 QSGMII Serdes, can rest Serdes be used for PCIe instance? How many 1 Lane PCIe instance supported?