Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello Team

I was testing the IPC Spinlock Shared memory example. The example works well on SK EVM

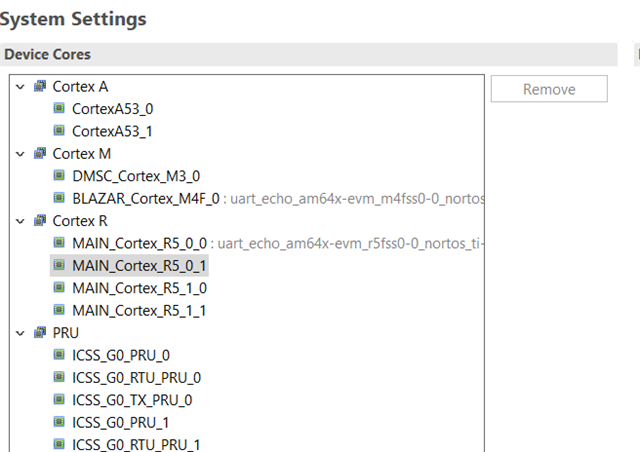

I want to add M4 core in this system project. I took the empty example for M4 core and reused the spinlock test code from other cores examples.

My question is:

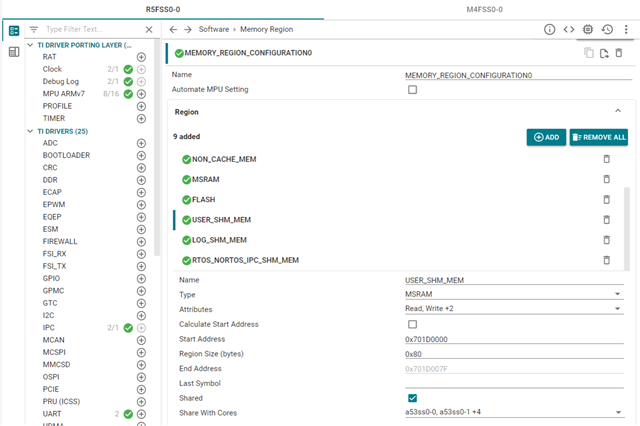

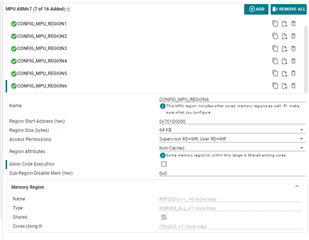

1. How do I configure the M4 core to use the same shared memory? What configuration do I have to do in .syscfg file?

2. In this example, we are sharing only a single variable (4 bytes long). How do I share a larger memory chunk say an array of 8 (4 bytes each)?

Thanks

Amey