Other Parts Discussed in Thread: TDA4VL

Tool/software:

Hi TI experts,

HW: our custom board

SDK: j721s2, 8.6

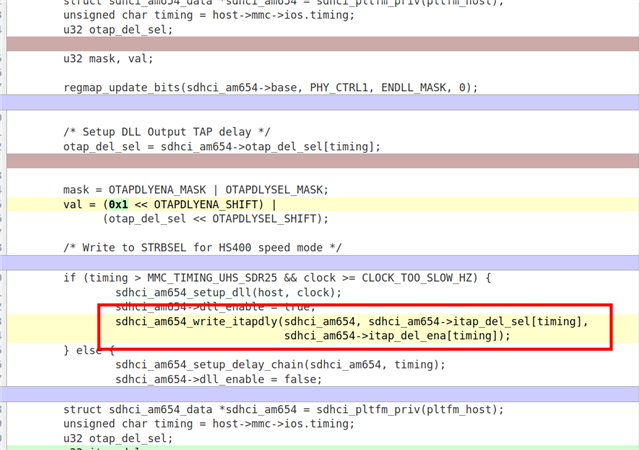

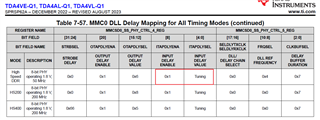

When we configure the eMMC to DDR52 mode, MMCSD0_SS_PHY_CTRL_4_REG @ 0x04F8810C value is 0x0010600A, which indicates that the input delay is not enabled, which is inconsistent with datasheet Table 7-57. How to configure ITAPDLYENA for DDR52? Is there a patch for this?

The following is the main_sdhci0 node of our devicetree.

main_sdhci0: mmc@4f80000 {

compatible = "ti,j721e-sdhci-8bit";

reg = <0x00 0x04f80000 0x00 0x1000>,

<0x00 0x04f88000 0x00 0x400>;

interrupts = <GIC_SPI 3 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 98 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 98 7>, <&k3_clks 98 1>;

clock-names = "clk_ahb", "clk_xin";

assigned-clocks = <&k3_clks 98 1>;

assigned-clock-parents = <&k3_clks 98 2>;

bus-width = <8>;

ti,otap-del-sel-legacy = <0x0>;

ti,otap-del-sel-mmc-hs = <0x0>;

ti,otap-del-sel-ddr52 = <0x6>;

// ti,otap-del-sel-hs200 = <0x8>;

// ti,otap-del-sel-hs400 = <0x5>;

ti,itap-del-sel-legacy = <0x10>;

ti,itap-del-sel-mmc-hs = <0xa>;

ti,strobe-sel = <0x77>;

ti,clkbuf-sel = <0x7>;

ti,trm-icp = <0x8>;

mmc-ddr-1_8v;

// mmc-hs200-1_8v;

// mmc-hs400-1_8v;

dma-coherent;

};

Thanks

Regards

quanfeng