Tool/software:

Hello Users,

Many users are asking to trigger DMA with the help of GPIO on AM64X/AM243 and AM62X devices.

So, I have created an example of this solution on AM64X and the procedure is the same for all other devices.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello Users,

Many users are asking to trigger DMA with the help of GPIO on AM64X/AM243 and AM62X devices.

So, I have created an example of this solution on AM64X and the procedure is the same for all other devices.

In this example, I have taken the source address is PSRAM memory location and the destination memory is DDR.

So, here users can use source and destination memory as per user requirements and memory addresses may be MSRAM / DDR /OSPI or any other memory.

Our devices can generate an DMA event from GPIO in both input or output modes .

The attached example below , I have used GPIO as an output and generating DMA event for every 1sec.

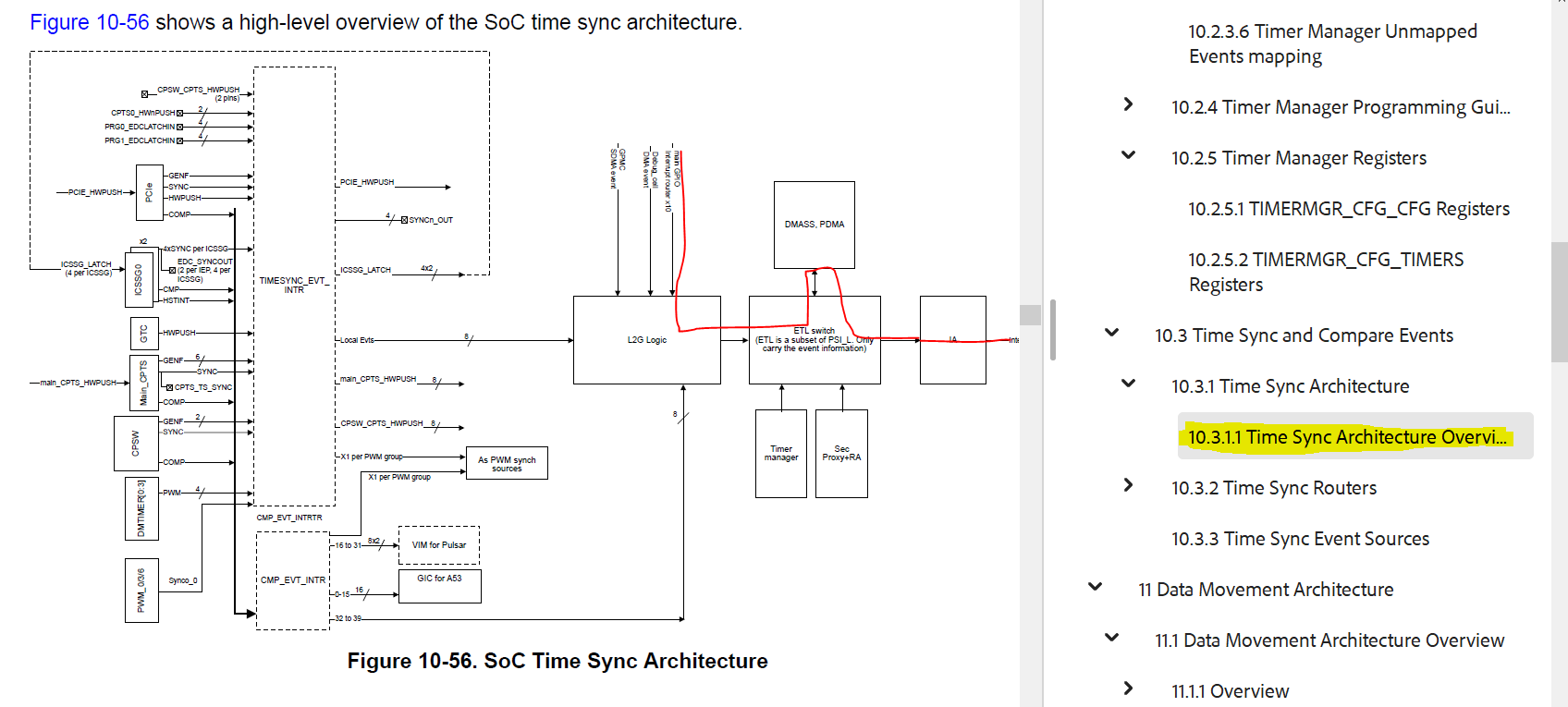

First go to the chapter below from TRM .

And, to trigger DMA from GPIO we need to follow the procedure below.

GPIO (Input/ Output) → RISING EDGE/ FALLING EDGE/ BOTH EDGES → GPIO MUX ROUTER → L2G (Local to Global Event) → DMSS / PDMA → IA → Destination core.

Steps :

1. Configuring GPIO Mux Router :

All GPIO interrupts should be routed to GPIO Mux router on AM64X.

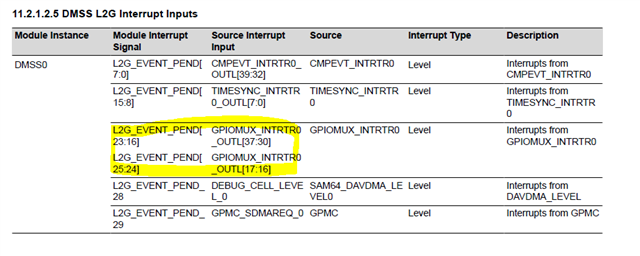

As per AM64X, to trigger DMA, on SOC total 10 router outputs are assigned.

Those are from 16 to 17 and 30 to 37 Router outputs are used to trigger DMA.

Please look at the image below .

So, users can allocate any router output and there are no issues.

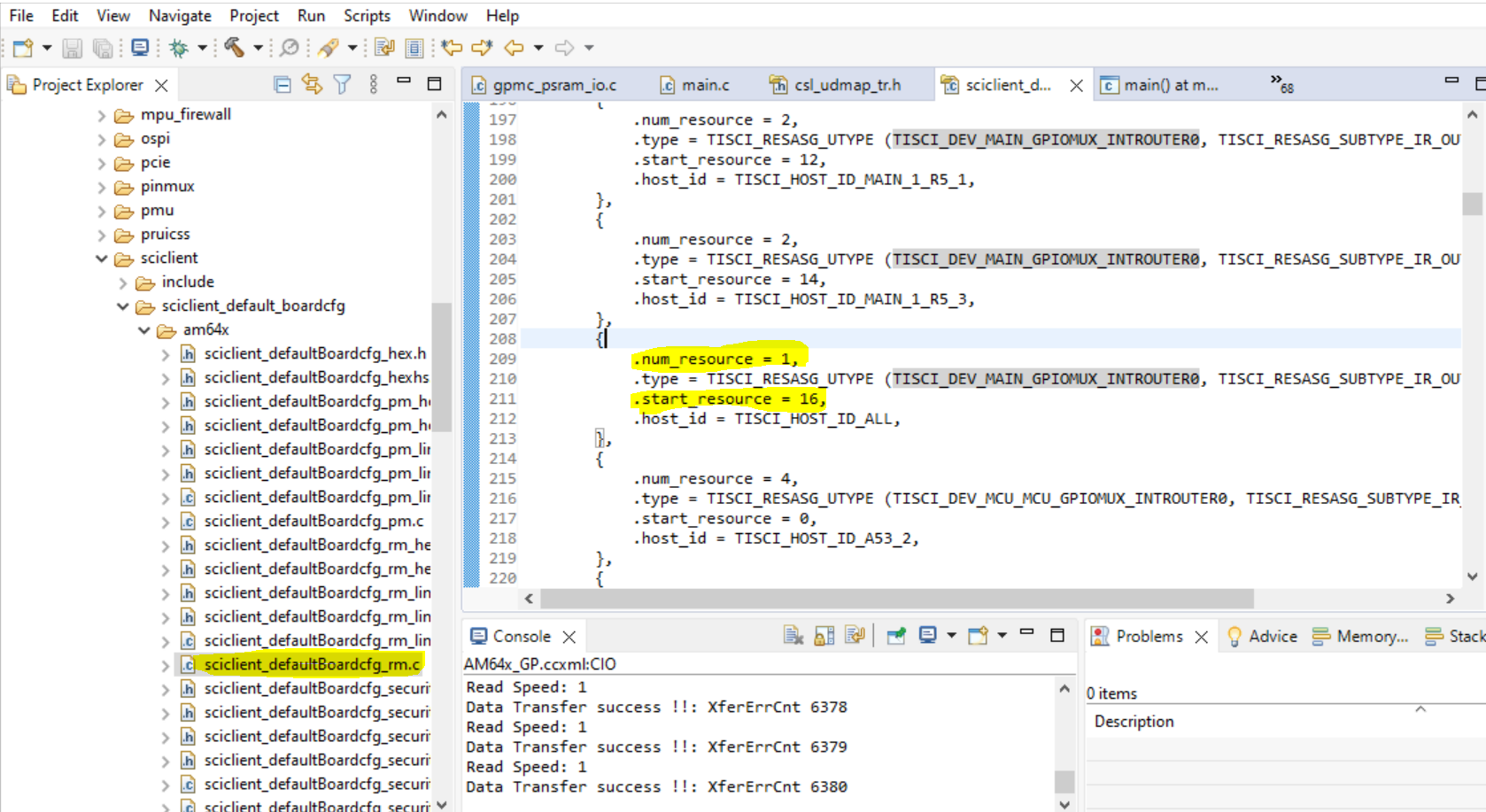

In the current example, I need only one router output for triggering DMA .So, I have chosen to 16th Router output and this router output should be configured in the sciclient_defaultBoardcfg_rm.file since currently, in the software, these routers are not configured.

So, I have updated only the GPIO-16 router in the sciclient_defaultBoardcfg_rm.c file.

Folder Path: C:timcu_plus_sdk_xx/source/drivers/sciclient/sciclient_default_boardcfgam64x_am243x

To update sciclient_defaultBoardcfg_rm.c file , please follow the procedure from the link below .

The sciclient_defaultBoardcfg_rm.c file is belongs to sysfw .So, user need to compile sciclient_defaultBoardcfg_rm.c file and after compilation it and sysfw should be flashed on SOC .

So, user should follow steps below .

a. Compile the sciclient_defaultBoardcfg_rm.c file.

b. Compile SBL and Flash SBL with updated board config file

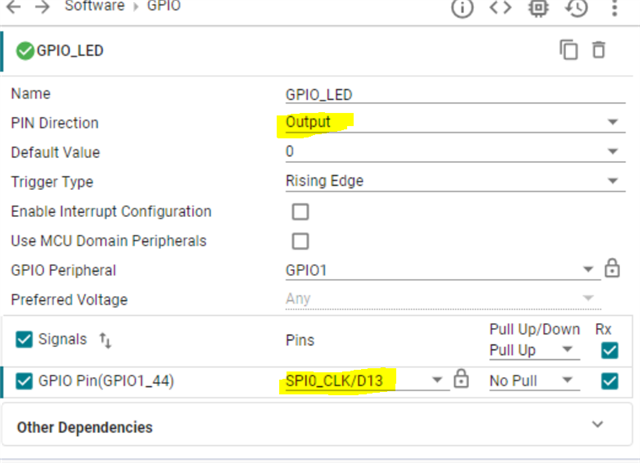

2. As I mentioned above, with the GPIO from either input or output configuration user can trigger DMA . In the attached example ,

I have choosen GPIO1_44 pin as output .

3. In the above steps , GPIO event is routed to a GPIO MUX router and now we need to convert this local event to global event .

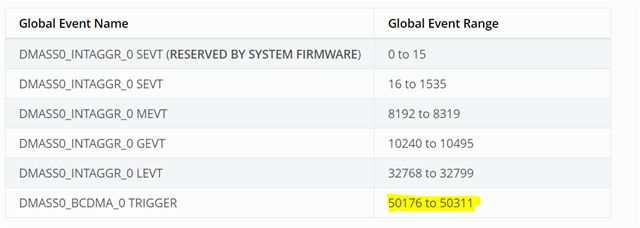

As per AM64X, the Global events started from 50176 and local events should be converted to the form of 50176+X.

Already in UDMA driver there is an API to convert a global event from local event , so users can just send the local event number.

4. Next, triggering DMA, here users need to configure below settings based on user requirements.

For example, users need to transfer from source to destination memory for less than 64KB then

If the data size is < 64KB, then

ICNT 0 = length and the trigger type is

pTr->flags |= CSL_FMK(UDMAP_TR_FLAGS_TRIGGER0, CSL_UDMAP_TR_FLAGS_TRIGGER_GLOBAL0);

pTr->flags |= CSL_FMK(UDMAP_TR_FLAGS_TRIGGER0_TYPE, CSL_UDMAP_TR_FLAGS_TRIGGER_TYPE_ICNT1_DEC);

If the data size is > 64KB, then

ICNT 0 and ICNT 1 should be configured accordingly to user length and the chosen trigger type is as below.

pTr->flags |= CSL_FMK(UDMAP_TR_FLAGS_TRIGGER0, CSL_UDMAP_TR_FLAGS_TRIGGER_GLOBAL0);

pTr->flags |= CSL_FMK(UDMAP_TR_FLAGS_TRIGGER0_TYPE, CSL_UDMAP_TR_FLAGS_TRIGGER_TYPE_ICNT2_DEC);

Example Code :

5023.gpmc_psram_io_am64x-evm_r5fss0-0_nortos_ti-arm-clang.zip

/*

* K3 System Firmware Resource Management Configuration Data

* Auto generated from K3 Resource Partitioning tool

*

* Copyright (c) 2018-2023, Texas Instruments Incorporated

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

*

* * Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

* AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

* THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

* PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR

* CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

* EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

* PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS;

* OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,

* WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR

* OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE,

* EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

/**

* \file sciclient_defaultBoardcfg_rm.c

*

* \brief File containing the rm boardcfg default data structure to

* send TISCI_MSG_BOARD_CONFIG_RM message.

*

*/

/* ========================================================================== */

/* Include Files */

/* ========================================================================== */

#include <drivers/sciclient.h>

#include <drivers/sciclient/include/tisci/am64x_am243x/tisci_hosts.h>

#include <drivers/sciclient/include/tisci/am64x_am243x/tisci_boardcfg_constraints.h>

#include <drivers/sciclient/include/tisci/am64x_am243x/tisci_devices.h>

/* ========================================================================== */

/* Global Variables */

/* ========================================================================== */

/* \brief Structure to hold the RM board configuration */

struct tisci_local_rm_boardcfg {

struct tisci_boardcfg_rm rm_boardcfg;

/**< Board configuration parameter */

struct tisci_boardcfg_rm_resasg_entry resasg_entries[TISCI_RESASG_ENTRIES_MAX];

/**< Resource assignment entries */

};

const struct tisci_local_rm_boardcfg gBoardConfigLow_rm

__attribute__(( aligned(128), section(".boardcfg_data") )) =

{

.rm_boardcfg = {

.rev = {

.tisci_boardcfg_abi_maj = TISCI_BOARDCFG_RM_ABI_MAJ_VALUE,

.tisci_boardcfg_abi_min = TISCI_BOARDCFG_RM_ABI_MIN_VALUE,

},

.host_cfg = {

.subhdr = {

.magic = TISCI_BOARDCFG_RM_HOST_CFG_MAGIC_NUM,

.size = (uint16_t) sizeof(struct tisci_boardcfg_rm_host_cfg),

},

.host_cfg_entries = {

{

.host_id = TISCI_HOST_ID_A53_2,

.allowed_atype = 0b101010,

.allowed_qos = 0xAAAA,

.allowed_orderid = 0xAAAAAAAA,

.allowed_priority = 0xAAAA,

.allowed_sched_priority = 0xAA

},

{

.host_id = TISCI_HOST_ID_M4_0,

.allowed_atype = 0b101010,

.allowed_qos = 0xAAAA,

.allowed_orderid = 0xAAAAAAAA,

.allowed_priority = 0xAAAA,

.allowed_sched_priority = 0xAA

},

{

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

.allowed_atype = 0b101010,

.allowed_qos = 0xAAAA,

.allowed_orderid = 0xAAAAAAAA,

.allowed_priority = 0xAAAA,

.allowed_sched_priority = 0xAA

},

{

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

.allowed_atype = 0b101010,

.allowed_qos = 0xAAAA,

.allowed_orderid = 0xAAAAAAAA,

.allowed_priority = 0xAAAA,

.allowed_sched_priority = 0xAA

},

{

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

.allowed_atype = 0b101010,

.allowed_qos = 0xAAAA,

.allowed_orderid = 0xAAAAAAAA,

.allowed_priority = 0xAAAA,

.allowed_sched_priority = 0xAA

},

{

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

.allowed_atype = 0b101010,

.allowed_qos = 0xAAAA,

.allowed_orderid = 0xAAAAAAAA,

.allowed_priority = 0xAAAA,

.allowed_sched_priority = 0xAA

},

},

},

.resasg = {

.subhdr = {

.magic = TISCI_BOARDCFG_RM_RESASG_MAGIC_NUM,

.size = (uint16_t) sizeof(struct tisci_boardcfg_rm_resasg),

},

.resasg_entries_size = 182 * sizeof(struct tisci_boardcfg_rm_resasg_entry),

},

},

.resasg_entries = {

{

.num_resource = 16,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_CMP_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_CMP_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 16,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_CMP_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 16,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_CMP_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 20,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_CMP_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 24,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_CMP_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 28,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_CMP_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 32,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MAIN_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MAIN_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 0,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MAIN_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 8,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MAIN_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 12,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MAIN_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 14,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MAIN_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 16,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MCU_MCU_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_MCU_MCU_GPIOMUX_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 4,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 41,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_TIMESYNC_EVENT_INTROUTER0, TISCI_RESASG_SUBTYPE_IR_OUTPUT),

.start_resource = 0,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 136,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_TRIGGER),

.start_resource = 50176,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_UDMAP_GLOBAL_CONFIG),

.start_resource = 0,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 12,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 12,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 12,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 18,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 20,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 24,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 26,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_BLOCK_COPY_CHAN),

.start_resource = 27,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_RX_CHAN),

.start_resource = 48,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_RX_CHAN),

.start_resource = 54,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_RX_CHAN),

.start_resource = 54,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_RX_CHAN),

.start_resource = 60,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_RX_CHAN),

.start_resource = 62,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_RX_CHAN),

.start_resource = 66,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_TX_CHAN),

.start_resource = 28,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_TX_CHAN),

.start_resource = 34,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_TX_CHAN),

.start_resource = 34,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_TX_CHAN),

.start_resource = 40,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_TX_CHAN),

.start_resource = 42,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_RING_SPLIT_TR_TX_CHAN),

.start_resource = 46,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 12,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 12,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 12,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 18,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 20,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 24,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 26,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_BLOCK_COPY_CHAN),

.start_resource = 27,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_RX_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_RX_CHAN),

.start_resource = 6,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_RX_CHAN),

.start_resource = 6,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_RX_CHAN),

.start_resource = 12,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_RX_CHAN),

.start_resource = 14,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_RX_CHAN),

.start_resource = 18,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_TX_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_TX_CHAN),

.start_resource = 6,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 6,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_TX_CHAN),

.start_resource = 6,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_TX_CHAN),

.start_resource = 12,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_TX_CHAN),

.start_resource = 14,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_BCDMA_0, TISCI_RESASG_SUBTYPE_BCDMA_SPLIT_TR_TX_CHAN),

.start_resource = 18,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 35,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_VINT),

.start_resource = 5,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 14,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_VINT),

.start_resource = 44,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 14,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_VINT),

.start_resource = 44,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 14,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_VINT),

.start_resource = 58,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 14,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_VINT),

.start_resource = 92,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 14,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_VINT),

.start_resource = 106,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 16,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_VINT),

.start_resource = 168,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 512,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 16,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 256,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 528,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 256,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 528,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 192,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 784,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 256,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 976,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 192,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 1232,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 96,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 1424,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 16,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_GLOBAL_EVENT_SEVT),

.start_resource = 1520,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 1024,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_TIMERMGR_EVT_OES),

.start_resource = 0,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 42,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_PKTDMA_TX_CHAN_ERROR_OES),

.start_resource = 4096,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 112,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_PKTDMA_TX_FLOW_COMPLETION_OES),

.start_resource = 4608,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 29,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_PKTDMA_RX_CHAN_ERROR_OES),

.start_resource = 5120,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 176,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_PKTDMA_RX_FLOW_COMPLETION_OES),

.start_resource = 5632,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 176,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_PKTDMA_RX_FLOW_STARVATION_OES),

.start_resource = 6144,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 176,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_PKTDMA_RX_FLOW_FIREWALL_OES),

.start_resource = 6656,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 28,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_CHAN_ERROR_OES),

.start_resource = 8192,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 28,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_CHAN_DATA_COMPLETION_OES),

.start_resource = 8704,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 28,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_CHAN_RING_COMPLETION_OES),

.start_resource = 9216,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 20,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_TX_CHAN_ERROR_OES),

.start_resource = 9728,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 20,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_TX_CHAN_DATA_COMPLETION_OES),

.start_resource = 10240,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 20,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_TX_CHAN_RING_COMPLETION_OES),

.start_resource = 10752,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 20,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_RX_CHAN_ERROR_OES),

.start_resource = 11264,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 20,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_RX_CHAN_DATA_COMPLETION_OES),

.start_resource = 11776,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 20,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_INTAGGR_0, TISCI_RESASG_SUBTYPE_IA_BCDMA_RX_CHAN_RING_COMPLETION_OES),

.start_resource = 12288,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_UDMAP_GLOBAL_CONFIG),

.start_resource = 0,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_TX_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_TX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_TX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_TX_CHAN),

.start_resource = 7,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_TX_CHAN),

.start_resource = 9,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_TX_CHAN),

.start_resource = 13,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_TX_CHAN),

.start_resource = 15,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_CPSW_TX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_CPSW_TX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_SAUL_TX_1_CHAN),

.start_resource = 88,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_SAUL_TX_1_CHAN),

.start_resource = 88,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_0_TX_CHAN),

.start_resource = 96,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_0_TX_CHAN),

.start_resource = 96,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_1_TX_CHAN),

.start_resource = 104,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_1_TX_CHAN),

.start_resource = 104,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_RX_CHAN),

.start_resource = 112,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_RX_CHAN),

.start_resource = 116,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_RX_CHAN),

.start_resource = 116,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_RX_CHAN),

.start_resource = 119,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_RX_CHAN),

.start_resource = 121,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_RX_CHAN),

.start_resource = 125,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_UNMAPPED_RX_CHAN),

.start_resource = 127,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 16,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_CPSW_RX_CHAN),

.start_resource = 128,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 16,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_CPSW_RX_CHAN),

.start_resource = 128,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_SAUL_RX_1_CHAN),

.start_resource = 144,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_SAUL_RX_2_CHAN),

.start_resource = 152,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_SAUL_RX_2_CHAN),

.start_resource = 152,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_SAUL_RX_3_CHAN),

.start_resource = 152,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_SAUL_RX_3_CHAN),

.start_resource = 152,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_0_RX_CHAN),

.start_resource = 160,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_0_RX_CHAN),

.start_resource = 160,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_1_RX_CHAN),

.start_resource = 224,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_RING_ICSSG_1_RX_CHAN),

.start_resource = 224,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_TX_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_TX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_TX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_TX_CHAN),

.start_resource = 7,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_TX_CHAN),

.start_resource = 9,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_TX_CHAN),

.start_resource = 13,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_TX_CHAN),

.start_resource = 15,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_CPSW_TX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_CPSW_TX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_SAUL_TX_1_CHAN),

.start_resource = 25,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_SAUL_TX_1_CHAN),

.start_resource = 25,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_0_TX_CHAN),

.start_resource = 26,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_0_TX_CHAN),

.start_resource = 26,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_1_TX_CHAN),

.start_resource = 34,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_1_TX_CHAN),

.start_resource = 34,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_RX_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_RX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_RX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_RX_CHAN),

.start_resource = 7,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_RX_CHAN),

.start_resource = 9,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_RX_CHAN),

.start_resource = 13,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_UNMAPPED_RX_CHAN),

.start_resource = 15,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_UNMAPPED_RX_CHAN),

.start_resource = 0,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_UNMAPPED_RX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 3,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_UNMAPPED_RX_CHAN),

.start_resource = 4,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_UNMAPPED_RX_CHAN),

.start_resource = 7,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_UNMAPPED_RX_CHAN),

.start_resource = 9,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_UNMAPPED_RX_CHAN),

.start_resource = 13,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_UNMAPPED_RX_CHAN),

.start_resource = 15,

.host_id = TISCI_HOST_ID_M4_0,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_CPSW_RX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_CPSW_RX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 16,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_CPSW_RX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 16,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_CPSW_RX_CHAN),

.start_resource = 16,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_SAUL_RX_0_CHAN),

.start_resource = 32,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_SAUL_RX_1_CHAN),

.start_resource = 32,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_SAUL_RX_2_CHAN),

.start_resource = 19,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_SAUL_RX_2_CHAN),

.start_resource = 19,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_SAUL_RX_2_CHAN),

.start_resource = 40,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_SAUL_RX_2_CHAN),

.start_resource = 40,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_SAUL_RX_3_CHAN),

.start_resource = 20,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_SAUL_RX_3_CHAN),

.start_resource = 20,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_SAUL_RX_3_CHAN),

.start_resource = 40,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 8,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_SAUL_RX_3_CHAN),

.start_resource = 40,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_0_RX_CHAN),

.start_resource = 21,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_0_RX_CHAN),

.start_resource = 21,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_ICSSG_0_RX_CHAN),

.start_resource = 48,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_ICSSG_0_RX_CHAN),

.start_resource = 48,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_1_RX_CHAN),

.start_resource = 25,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_ICSSG_1_RX_CHAN),

.start_resource = 25,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_ICSSG_1_RX_CHAN),

.start_resource = 112,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 64,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_PKTDMA_0, TISCI_RESASG_SUBTYPE_PKTDMA_FLOW_ICSSG_1_RX_CHAN),

.start_resource = 112,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 1,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_ERROR_OES),

.start_resource = 0,

.host_id = TISCI_HOST_ID_ALL,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_VIRTID),

.start_resource = 2,

.host_id = TISCI_HOST_ID_A53_2,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_GENERIC_IPC),

.start_resource = 20,

.host_id = TISCI_HOST_ID_MAIN_0_R5_0,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_GENERIC_IPC),

.start_resource = 20,

.host_id = TISCI_HOST_ID_MAIN_0_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_GENERIC_IPC),

.start_resource = 22,

.host_id = TISCI_HOST_ID_MAIN_0_R5_3,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_GENERIC_IPC),

.start_resource = 24,

.host_id = TISCI_HOST_ID_MAIN_1_R5_1,

},

{

.num_resource = 2,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_GENERIC_IPC),

.start_resource = 26,

.host_id = TISCI_HOST_ID_MAIN_1_R5_3,

},

{

.num_resource = 4,

.type = TISCI_RESASG_UTYPE (TISCI_DEV_DMASS0_RINGACC_0, TISCI_RESASG_SUBTYPE_RA_GENERIC_IPC),

.start_resource = 28,

.host_id = TISCI_HOST_ID_ALL,

},

}

};

If users still need help on this topic please raise new threads .

I have verified the basic functionality and not checked in all other Testcases .

Please do Testing while integrating these changes in your application .

As per TRM, routing GPIO interrupt to L2G is Level Type.

For the level type, we need to set 1 in the L2G Register, but in the above example, I set the pulse type and configured to zero.

Please change the API definition in the example with the change below.

static void configure_intaggrL2G(uint32_t localEvent, uint32_t globalEvent)

{

uint64_t eventRegOffset = CSL_DMASS0_INTAGGR_L2G_BASE + (localEvent * 0x20U);

CSL_REG64_WR(eventRegOffset, ( (1U << 31U) | (globalEvent & 0xFFFFU) ) ); /* Level event */

}