Other Parts Discussed in Thread: AM620, DP83869

Tool/software:

If I enable eth1 in * uboot.dtsi, why can I not make it "active'?

How do I enable the second ethernet port? I'm assuming it's done using "k3-am62x-sk-common-u-boot.dtsi". I made a change here to see the above in u-boot shell but I think I'm missing some configuration info. Here's my "k3-am62x-sk-common-u-boot.dtsi" file:

// SPDX-License-Identifier: GPL-2.0

/*

* Common AM62x SK dts file for SPLs

* Copyright (C) 2021-2022 Texas Instruments Incorporated - https://www.ti.com/

*/

/ {

chosen {

stdout-path = "serial2:115200n8";

tick-timer = &timer1;

};

aliases {

mmc0 = &sdhci0;

mmc1 = &sdhci1;

};

memory@80000000 {

bootph-pre-ram;

};

};

&cbass_main{

bootph-pre-ram;

timer1: timer@2400000 {

clock-frequency = <25000000>;

bootph-pre-ram;

};

};

&dmss {

bootph-pre-ram;

};

&secure_proxy_main {

bootph-pre-ram;

};

&dmsc {

bootph-pre-ram;

k3_sysreset: sysreset-controller {

compatible = "ti,sci-sysreset";

bootph-pre-ram;

};

};

&k3_pds {

bootph-pre-ram;

};

&k3_clks {

bootph-pre-ram;

};

&k3_reset {

bootph-pre-ram;

};

&wkup_conf {

bootph-pre-ram;

};

&chipid {

bootph-pre-ram;

};

&main_pmx0 {

bootph-pre-ram;

};

&main_uart0 {

bootph-pre-ram;

};

&main_uart0_pins_default {

bootph-pre-ram;

};

&main_uart1 {

bootph-pre-ram;

};

&cbass_mcu {

bootph-pre-ram;

};

&cbass_wakeup {

bootph-pre-ram;

};

&mcu_pmx0 {

bootph-pre-ram;

};

&wkup_uart0 {

bootph-pre-ram;

};

&main_i2c0 {

bootph-pre-ram;

};

&main_i2c0_pins_default {

bootph-pre-ram;

};

&sdhci0 {

bootph-pre-ram;

};

&sdhci1 {

bootph-pre-ram;

};

&main_mmc1_pins_default {

bootph-pre-ram;

};

&usbss0 {

bootph-pre-ram;

};

&usb0 {

dr_mode = "peripheral";

/* Since role switching is not supported in U-Boot */

/delete-property/ extcon;

bootph-pre-ram;

};

&usbss1 {

bootph-pre-ram;

};

&usb1 {

bootph-pre-ram;

};

&main_usb1_pins_default {

bootph-pre-ram;

};

&cpsw3g {

reg = <0x0 0x8000000 0x0 0x200000>,

<0x0 0x43000200 0x0 0x8>;

reg-names = "cpsw_nuss", "mac_efuse";

/delete-property/ ranges;

/* This is WA because MDIO driver is not DM enabled */

pinctrl-0 = <&main_mdio1_pins_default &main_rgmii1_pins_default>;

bootph-pre-ram;

cpsw-phy-sel@04044 {

compatible = "ti,am64-phy-gmii-sel";

reg = <0x0 0x00104044 0x0 0x8>;

bootph-pre-ram;

};

};

//&cpsw_port2 {

// JM status = "disabled";

// bootph-pre-ram;

//};

&main_bcdma {

bootph-pre-ram;

reg = <0x00 0x485c0100 0x00 0x100>,

<0x00 0x4c000000 0x00 0x20000>,

<0x00 0x4a820000 0x00 0x20000>,

<0x00 0x4aa40000 0x00 0x20000>,

<0x00 0x4bc00000 0x00 0x100000>,

<0x00 0x48600000 0x00 0x8000>,

<0x00 0x484a4000 0x00 0x2000>,

<0x00 0x484c2000 0x00 0x2000>;

reg-names = "gcfg", "bchanrt", "rchanrt", "tchanrt",

"ringrt" , "cfg", "tchan", "rchan";

};

&main_pktdma {

bootph-pre-ram;

reg = <0x00 0x485c0000 0x00 0x100>,

<0x00 0x4a800000 0x00 0x20000>,

<0x00 0x4aa00000 0x00 0x20000>,

<0x00 0x4b800000 0x00 0x200000>,

<0x00 0x485e0000 0x00 0x10000>,

<0x00 0x484a0000 0x00 0x2000>,

<0x00 0x484c0000 0x00 0x2000>,

<0x00 0x48430000 0x00 0x1000>;

reg-names = "gcfg", "rchanrt", "tchanrt", "ringrt",

"cfg", "tchan", "rchan", "rflow";

};

&fss {

bootph-pre-ram;

};

&cpsw_port1 {

bootph-pre-ram;

};

// JM

&cpsw_port2 {

bootph-pre-ram;

};

// end

&main_rgmii1_pins_default {

bootph-pre-ram;

};

// JM

//&main_rgmii2_pins_default {

// bootph-pre-ram;

//};

// end

&main_mdio1_pins_default {

bootph-pre-ram;

};

&cpsw3g_phy0 {

bootph-pre-ram;

};

// JM

//&cpsw3g_phy1 {

// bootph-pre-ram;

//};

// end

&dmsc {

bootph-pre-ram;

k3_sysreset: sysreset-controller {

compatible = "ti,sci-sysreset";

bootph-pre-ram;

};

};

&main_gpio0 {

bootph-pre-ram;

};

&main_i2c1 {

bootph-pre-ram;

};

&main_i2c1_pins_default {

bootph-pre-ram;

};

&exp1 {

bootph-pre-ram;

};

&vdd_mmc1 {

bootph-pre-ram;

};

USB0 should be started by default, correct? We don't have a usbc device on USB0, just a standard USBA connection. Any changes required there in the file, as well?

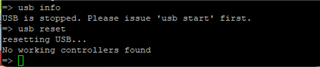

Right now I get the following: