Other Parts Discussed in Thread: TMUX1308, AM625, TMUX1308A, SN74LV4051A, TMUX1308A-Q1, ADC121S101, , TPS65224-Q1

Tool/software:

Hi Team,

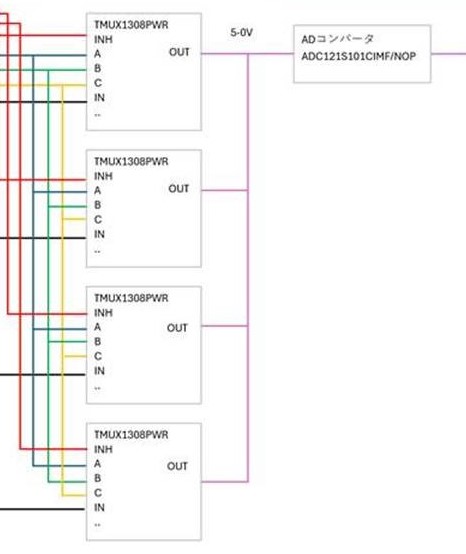

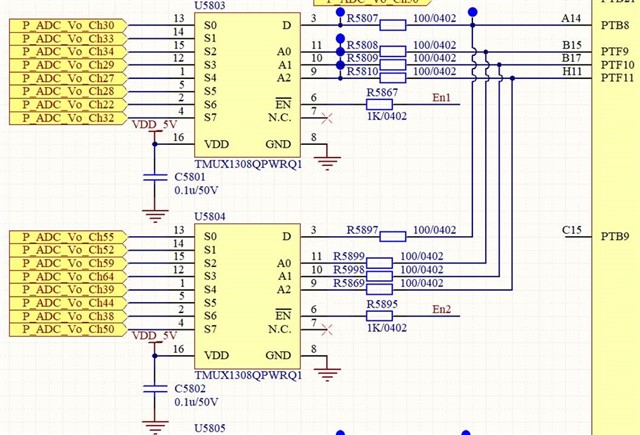

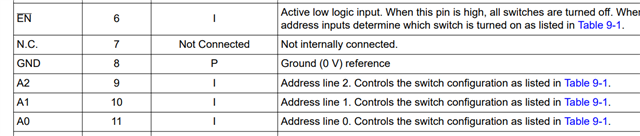

TMUX1308 EN and control A0..A2 is being controlled by AM625 Sitara SOC.

SOC IO buffers are off during power-up. The IOs are in high impedance and expected to take 1..2 seconds to be initialized to a known state.

Do you have any recommendation of connecting the EN and the control inputs during this period.

Are the TMUX EN and address control inputs A0..2 tolerant to being open for some time ( 1..2 sec) during power cycle until the SOC IOs are initialized.

Thank you for the support.

Regards,

Sreenivasa