Part Number: PROCESSOR-SDK-AM335X

Tool/software:

Dear TI Support,

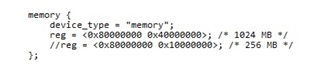

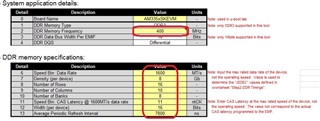

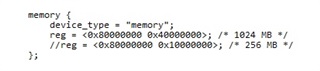

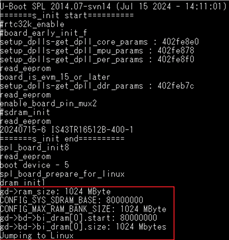

I am currently using an AM335x processor with SDK version 02.00.02.11 and am seeking recommendations for a compatible 1GB DDR memory module.

During testing, I am trying to upgrade from a 4GB to an 8GB module, but the system only recognizes 4GB.

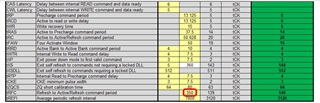

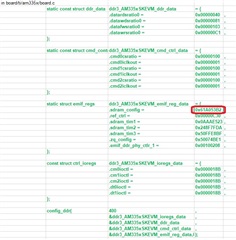

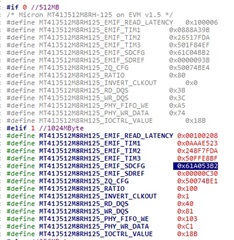

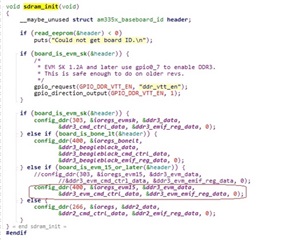

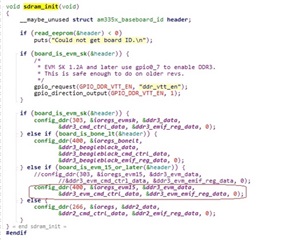

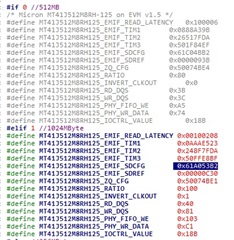

Currently, the sdram_config is set to MT41J512M8H125_EMIF_SDCONF. I would like to test with MT41J512M16H125_EMIF_SDCONF (16-bit) configuration.

Is this supported?

I could not find relevant information for this configuration in the current SDK.

I would appreciate your assistance on this matter.

Thank you.

Best regards,