Tool/software:

Hallo,

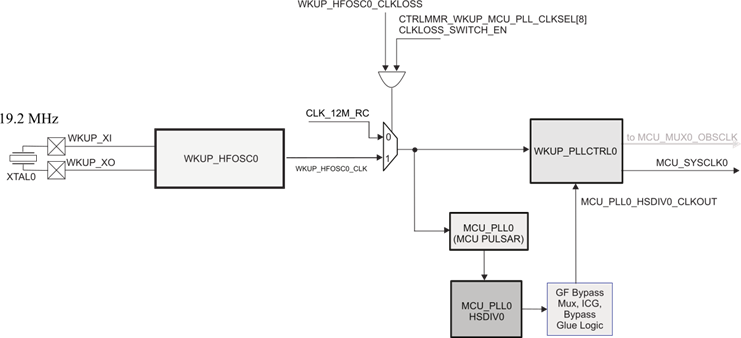

for the clock and PLL we have followed question to make clarfiy the seq. of the PLL setting and Sys clock in MCU domain, which also impact on the MCAL config. like WDT and GPT

based on our understanding form Technical Documentation, the 19.2 MHz is selected. As my understanding from TI, that the WKUP_HFOSC0, MCU_PLL0 and WKUP_PLL_CTRL0 is done by ROM code at begin(R5 first PLL lock by DMSC). After boot up, it can not be changed, even register of those PLL has description. Then what is the output freq. of MCU_SYSCLK0?

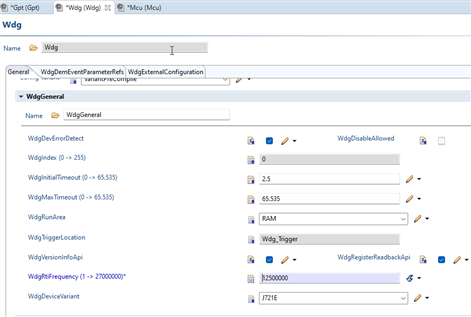

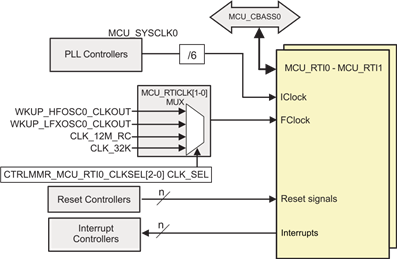

After MCU_SYSCLK0 is confirmed, then to the WDG in MCU Domain.(RTI). As my understanding the Functional Clock is used for the setting of the watchdog time. Interface Clock --> what is usage? For the MCAL config. which freq. of the clock has impact to the configuration?

WdgRtiFrequency is default with 12.5MHz (internal CLK_12M_RC)? this freqency setting is based on which clock? also for later GPT timer. How does the clock impact those configuration (principal)?