Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello,

I have a question regarding the GPIO interrupt configuration procedure on the AM243x.

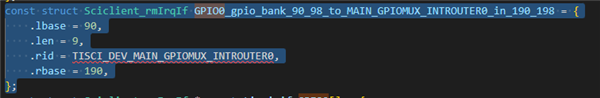

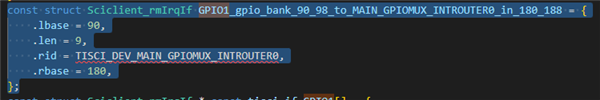

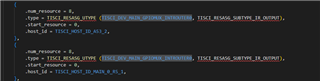

Below is the SciClient message that gets generate to enable the interrupt on a given GPIO based on the files generated from the SysConfig tool

However, the function asserts when I run this on our chip.

After some investigation, I found that there are different values for the interrupt routers that can be used based on which GPIO is being configured.

There's these ones in the cslr_intr_r5fss0_core0.h

And then theres an interrupt router defined for each GPIOs in the cslr_intr_main_gpiomux_introuter0.h

as well as routers specifically for each GPIO bank

Which one should I use?

Thanks!

Eden