Tool/software:

Hello,

Board: J784s4 custom board

PDK: 09.02.00.30

Linux

SPL Boot

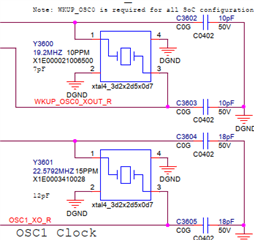

To achieve it I have seen that following PLLs base clock oscillator have to be switched

PLL0 (MAIN PLL) -> MAIN_PLL0_HSDIV6_CLKOUT -> GTC Timer

PLL8 (ARM0 PLL - A72 cluster 0)

PLL9 (ARM1 PLL - A72 cluster 1)

PLL14(R5FSS PLL - R5F main domain)

Our current setup is, that at in the MCU 1_0 firmware the MAIN domain PLL's are initialized by the assistant of the sciclient -> running at the default HFOSC0

Afterward the registers of the concerning PLLs are modified with:

-> enable HFSOC1 oscillator

-> disable PLL0, PLL8 and PLL9.

-> switch base oscillator to hfsoc1

-> adjust gain to get from 22579200Hz to 2GHZ

-> enable PLLs again and wait for LOCK.

( "packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j784s4/clocks.c")

Following routine, located at ("packages/ti/drv/sciclient/src/rm_pm_hal/pm/drivers/clock"), is responsible to setup the PLLs depending

static u32 clk_pll_16fft_internal_set_freq_from_pll_table(struct clk *pll_clk, struct clk *div_clk, const struct pll_data *pll_data_t, u32 target_hz, u32 min_hz, u32 max_hz, sbool query, sbool *changed)

If yes do you have any patch or some tips what have to be done?

Kind Regards

Thomas Willetal