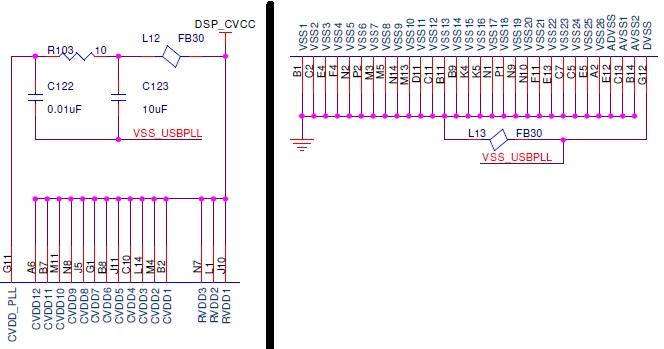

Perusing the 553x data sheet, I noticed that these devices have dedicated power and ground pins for the system clock PLL. That made me wonder: What power and ground pins are associated with the system clock PLL on the 5509A? Experience has shown that the PLL in this part is rather prone to losing lock, so it would be desirable to provide some extra filtering on its supply. Are there specific pins that power this? There's no mention in the data sheet.

David