Other Parts Discussed in Thread: TDA4VL, TDA4VM

Tool/software:

Hi expert,

Our customer is using TDA4VL SDK0806. They found the operation of MAIN domain will impact the MCU1_0 task cycle and the issue disappear when moving the MCU code to MSMC. So they suspect this is caused by the priority of DDR access.

They also test the DDR bandwidth by the ti perf. The actual bandwidth is below 8GB/s. So we think the DDR bandwidth still have some buffer. They once used TDA4VM SDK7.3 and didn't run into similar issue.

They referd to below 2 thread and added the NB and QoS config for the MCU, but it didn't work.

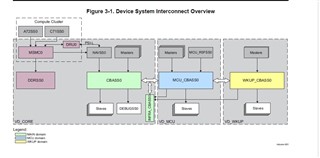

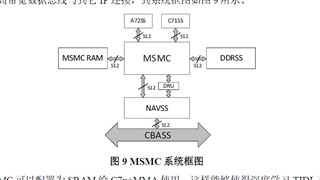

As shown in the below diagram, there are CBASS, NAVSS, MSMC and DDSS, and DDRSS is only connected to MSMC. Customer would like to know:

1. Regarding the above 2 patches, what is the function of NB and QoS config? Can it help MCU access DDR?

2. Besides the QoS, it there any other points they need to care and check?

Best Regards,

Xingyu Zhu