Other Parts Discussed in Thread: SK-AM62-LP

Tool/software:

what settings needed in kernel configuration ?

what changes needed in dts file, i want 16 bit interface. please provide relevant thread or document.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

what settings needed in kernel configuration ?

what changes needed in dts file, i want 16 bit interface. please provide relevant thread or document.

Hi,

Here are the GPMC device tree bindings documentation in kernel:

Documentation/devicetree/bindings/memory-controllers/ti,gpmc.yaml

Documentation/devicetree/bindings/memory-controllers/ti,gpmc-child.yaml

Documentation/devicetree/bindings/mtd/ti,gpmc-nand.yaml

Here is the kernel AM625 LP EVM nand overlay device tree file which can be used as an example.

arch/arm64/boot/dts/ti/k3-am62-lp-sk-nand.dtso

Please check the another kernel dts arch/arm64/boot/dts/ti/k3-am642-evm-nand.dtso. It is for 16bit mode, but on CS0.

This is for AM64x devices, which has the same GPMC controller as that on AM625.

I'm configuring GPMC0 for a 4MB SRAM (CS2) on a Phytec AM62x. After updating the DTS file, I'm getting a bus error with devmem2. Could this error be due to the physical memory bus not being connected, or could it be a different issue? Any suggestions for troubleshooting?

or

how i can monitor GPMC is properly enabled? without hardware interfacing?

Thanks!

Does the kernel log has any message related to GPMC?

Please show your devmem2 command log. I'd like to see what address you try to read.

// SPDX-License-Identifier: GPL-2.0

/*

* Copyright (C) 2022-2023 Texas Instruments Incorporated - https://www.ti.com/

*/

/dts-v1/;

/plugin/;

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

#include "k3-pinctrl.h"

&mcasp1 {

status = "disabled";

};

&main_pmx0 {

gpmc0_pins_default: gpmc0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x003c, PIN_INPUT, 0) /* (M25) GPMC0_AD0 */

AM62X_IOPAD(0x0040, PIN_INPUT, 0) /* (N23) GPMC0_AD1 */

AM62X_IOPAD(0x0044, PIN_INPUT, 0) /* (N24) GPMC0_AD2 */

AM62X_IOPAD(0x0048, PIN_INPUT, 0) /* (N25) GPMC0_AD3 */

AM62X_IOPAD(0x004c, PIN_INPUT, 0) /* (P24) GPMC0_AD4 */

AM62X_IOPAD(0x0050, PIN_INPUT, 0) /* (P22) GPMC0_AD5 */

AM62X_IOPAD(0x0054, PIN_INPUT, 0) /* (P21) GPMC0_AD6 */

AM62X_IOPAD(0x0058, PIN_INPUT, 0) /* (R23) GPMC0_AD7 */

AM62X_IOPAD(0x0084, PIN_OUTPUT, 0) /* (L23) GPMC0_ADVn_ALE */

AM62X_IOPAD(0x0088, PIN_OUTPUT, 0) /* (L24) GPMC0_OEn_REn */

AM62X_IOPAD(0x008c, PIN_OUTPUT, 0) /* (L25) GPMC0_WEn */

AM62X_IOPAD(0x0090, PIN_OUTPUT, 0) /* (M24) GPMC0_BE0n_CLE */

AM62X_IOPAD(0x00a8, PIN_OUTPUT, 0) /* (M21) GPMC0_CSn0 */

AM62X_IOPAD(0x0098, PIN_INPUT, 0) /* (U23) GPMC0_WAIT0 */

>;

};

};

&gpmc0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&gpmc0_pins_default>;

ranges = <0 0 0x00 0x51000000 0x01000000>; /* CS0 space. Min partition = 16MB */

#address-cells = <2>;

#size-cells = <1>;

nand0_0: nand@0,0 {

compatible = "ti,am64-nand";

reg = <0 0 64>; /* device IO registers */

interrupt-parent = <&gpmc0>;

interrupts = <0 IRQ_TYPE_NONE>, /* fifoevent */

<1 IRQ_TYPE_NONE>; /* termcount */

rb-gpios = <&gpmc0 0 GPIO_ACTIVE_HIGH>; /* gpmc_wait0 */

ti,nand-xfer-type = "prefetch-polled";

ti,nand-ecc-opt = "bch8"; /* BCH8: Bootrom limitation */

ti,elm-id = <&elm0>;

nand-bus-width = <8>;

gpmc,device-width = <1>;

gpmc,sync-clk-ps = <0>;

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <40>;

gpmc,cs-wr-off-ns = <40>;

gpmc,adv-on-ns = <0>;

gpmc,adv-rd-off-ns = <25>;

gpmc,adv-wr-off-ns = <25>;

gpmc,we-on-ns = <0>;

gpmc,we-off-ns = <20>;

gpmc,oe-on-ns = <3>;

gpmc,oe-off-ns = <30>;

gpmc,access-ns = <30>;

gpmc,rd-cycle-ns = <40>;

gpmc,wr-cycle-ns = <40>;

gpmc,bus-turnaround-ns = <0>;

gpmc,cycle2cycle-delay-ns = <0>;

gpmc,clk-activation-ns = <0>;

gpmc,wr-access-ns = <40>;

gpmc,wr-data-mux-bus-ns = <0>;

partitions {

compatible = "fixed-partitions";

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "NAND.tiboot3";

reg = <0x00000000 0x00200000>; /* 2M */

};

partition@200000 {

label = "NAND.tispl";

reg = <0x00200000 0x00200000>; /* 2M */

};

partition@400000 {

label = "NAND.tiboot3.backup"; /* 2M */

reg = <0x00400000 0x00200000>; /* BootROM looks at 4M */

};

partition@600000 {

label = "NAND.u-boot";

reg = <0x00600000 0x00400000>; /* 4M */

};

partition@a00000 {

label = "NAND.u-boot-env";

reg = <0x00a00000 0x00040000>; /* 256K */

};

partition@a40000 {

label = "NAND.u-boot-env.backup";

reg = <0x00a40000 0x00040000>; /* 256K */

};

partition@a80000 {

label = "NAND.file-system";

reg = <0x00a80000 0x3f580000>;

};

};

};

};

&elm0{

status = "okay";

};

above .dts file using just for testing.

Can not find any gpmc related message:

root@phyboard-lyra-am62xx-3:~# devmem2 0x51000000

/dev/mem opened.

Memory mapped at address 0xffff8737e000.

Bus error

root@phyboard-lyra-am62xx-3:~# dmesg | grep gpmc

root@phyboard-lyra-am62xx-3:~#

root@phyboard-lyra-am62xx-3:~# dmesg | grep gpmc

root@phyboard-lyra-am62xx-3:~#

This basically means GPMC is not enumerated. I am getting the following message on SK-AM62-LP with k3-am62-lp-sk-nand.dtbo overlay.

root@am62xx-evm:~# dmesg|grep gpmc [ 0.210802] omap-gpmc 3b000000.memory-controller: GPMC revision 6.0 [ 0.210826] gpmc_mem_root start 0x50000000, end 0x57ffffff, cs 0, base 0x11000000, size 0x1000000 [ 0.210835] gpmc_mem_init: disabling cs 0 mapped at 0x11000000-0x12000000

The DTS file you provided above looks like a overlay file. How did you exactly use it on your board? Please provide the command or log if necessary to show the details.

// SPDX-License-Identifier: GPL-2.0

/*

* Copyright (C) 2022 - 2023 PHYTEC Messtechnik GmbH

* Author: Wadim Egorov <w.egorov@phytec.de>

*

* Product homepage:

* https://www.phytec.com/product/phyboard-am62x

*/

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/input/input.h>

#include <dt-bindings/leds/common.h>

#include <dt-bindings/net/ti-dp83867.h>

#include "k3-am625.dtsi"

#include "k3-am62-phycore-som.dtsi"

/ {

compatible = "phytec,am625-phyboard-lyra-rdk",

"phytec,am62-phycore-som", "ti,am625";

model = "PHYTEC phyBOARD-Lyra AM625";

aliases {

serial2 = &main_uart0;

serial3 = &main_uart1;

mmc1 = &sdhci1;

usb0 = &usb0;

usb1 = &usb1;

ethernet1 = &cpsw_port2;

};

can_tc1: can-phy0 {

compatible = "ti,tcan1042";

#phy-cells = <0>;

max-bitrate = <8000000>;

standby-gpios = <&gpio_exp 1 GPIO_ACTIVE_HIGH>;

};

hdmi0: connector-hdmi {

compatible = "hdmi-connector";

label = "hdmi";

type = "a";

port {

hdmi_connector_in: endpoint {

remote-endpoint = <&sii9022_out>;

};

};

};

keys {

compatible = "gpio-keys";

autorepeat;

pinctrl-names = "default";

pinctrl-0 = <&gpio_keys_pins_default>;

key-home {

label = "home";

linux,code = <KEY_HOME>;

gpios = <&main_gpio1 23 GPIO_ACTIVE_HIGH>;

};

key-menu {

label = "menu";

linux,code = <KEY_MENU>;

gpios = <&gpio_exp 4 GPIO_ACTIVE_HIGH>;

};

};

codec_audio: sound {

compatible = "simple-audio-card";

simple-audio-card,name = "phyBOARD-Lyra";

simple-audio-card,widgets =

"Microphone", "Mic Jack",

"Headphone", "Headphone Jack",

"Speaker", "External Speaker";

simple-audio-card,routing =

"MIC3R", "Mic Jack",

"Mic Jack", "Mic Bias",

"Headphone Jack", "HPLOUT",

"Headphone Jack", "HPROUT",

"External Speaker", "SPOP",

"External Speaker", "SPOM";

simple-audio-card,format = "dsp_b";

simple-audio-card,bitclock-master = <&sound_master>;

simple-audio-card,frame-master = <&sound_master>;

simple-audio-card,bitclock-inversion;

simple-audio-card,cpu {

sound-dai = <&mcasp2>;

};

sound_master: simple-audio-card,codec {

sound-dai = <&audio_codec>;

clocks = <&audio_refclk1>;

system-clock-frequency = <19200000>;

};

};

leds {

compatible = "gpio-leds";

pinctrl-names = "default";

pinctrl-0 = <&leds_pins_default>, <&user_leds_pins_default>;

led-1 {

gpios = <&main_gpio0 32 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "mmc0";

linux,default-trigger = "heartbeat";

};

led-2 {

gpios = <&gpio_exp 2 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "mmc1";

};

};

vcc_1v8: regulator-vcc-1v8 {

compatible = "regulator-fixed";

regulator-name = "VCC_1V8";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

regulator-always-on;

regulator-boot-on;

};

vcc_3v3_mmc: regulator-vcc-3v3-mmc {

compatible = "regulator-fixed";

regulator-name = "VCC_3V3_MMC";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

regulator-boot-on;

};

vcc_3v3_sw: regulator-vcc-3v3-sw {

compatible = "regulator-fixed";

regulator-name = "VCC_3V3_SW";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

regulator-boot-on;

};

};

&main_pmx0 {

audio_ext_refclk1_pins_default: audio-ext-refclk1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x0a0, PIN_OUTPUT, 1) /* (K25) GPMC0_WPn.AUDIO_EXT_REFCLK1 */

>;

};

gpio_keys_pins_default: gpio-keys-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1d4, PIN_INPUT, 7) /* (B15) UART0_RTSn.GPIO1_23 */

>;

};

hdmi_int_pins_default: hdmi-int-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x040, PIN_INPUT, 7) /* (N23) GPMC0_AD1.GPIO0_16 */

>;

};

gpio_exp_int_pins_default: gpio-exp-int-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x244, PIN_INPUT, 7) /* (C17) MMC1_SDWP.GPIO1_49 */

>;

};

main_dss0_pins_default: main-dss0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x0b8, PIN_OUTPUT, 0) /* (U22) VOUT0_DATA0 */

AM62X_IOPAD(0x0bc, PIN_OUTPUT, 0) /* (V24) VOUT0_DATA1 */

AM62X_IOPAD(0x0e0, PIN_OUTPUT, 0) /* (V20) VOUT0_DATA10 */

AM62X_IOPAD(0x0e4, PIN_OUTPUT, 0) /* (AA23) VOUT0_DATA11 */

AM62X_IOPAD(0x0e8, PIN_OUTPUT, 0) /* (AB25) VOUT0_DATA12 */

AM62X_IOPAD(0x0ec, PIN_OUTPUT, 0) /* (AA24) VOUT0_DATA13 */

AM62X_IOPAD(0x0f0, PIN_OUTPUT, 0) /* (Y22) VOUT0_DATA14 */

AM62X_IOPAD(0x0f4, PIN_OUTPUT, 0) /* (AA21) VOUT0_DATA15 */

AM62X_IOPAD(0x0c0, PIN_OUTPUT, 0) /* (W25) VOUT0_DATA2 */

AM62X_IOPAD(0x0c4, PIN_OUTPUT, 0) /* (W24) VOUT0_DATA3 */

AM62X_IOPAD(0x0c8, PIN_OUTPUT, 0) /* (Y25) VOUT0_DATA4 */

AM62X_IOPAD(0x0cc, PIN_OUTPUT, 0) /* (Y24) VOUT0_DATA5 */

AM62X_IOPAD(0x0d0, PIN_OUTPUT, 0) /* (Y23) VOUT0_DATA6 */

AM62X_IOPAD(0x0d4, PIN_OUTPUT, 0) /* (AA25) VOUT0_DATA7 */

AM62X_IOPAD(0x0d8, PIN_OUTPUT, 0) /* (V21) VOUT0_DATA8 */

AM62X_IOPAD(0x0dc, PIN_OUTPUT, 0) /* (W21) VOUT0_DATA9 */

AM62X_IOPAD(0x0fc, PIN_OUTPUT, 0) /* (Y20) VOUT0_DE */

AM62X_IOPAD(0x0f8, PIN_OUTPUT, 0) /* (AB24) VOUT0_HSYNC */

AM62X_IOPAD(0x104, PIN_OUTPUT, 0) /* (AC24) VOUT0_PCLK */

AM62X_IOPAD(0x100, PIN_OUTPUT, 0) /* (AC25) VOUT0_VSYNC */

>;

};

gpmc0_pins_default: gpmc0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x003c, PIN_INPUT, 0) /* (M25) GPMC0_AD0 */

AM62X_IOPAD(0x0040, PIN_INPUT, 0) /* (N23) GPMC0_AD1 */

AM62X_IOPAD(0x0044, PIN_INPUT, 0) /* (N24) GPMC0_AD2 */

AM62X_IOPAD(0x0048, PIN_INPUT, 0) /* (N25) GPMC0_AD3 */

AM62X_IOPAD(0x004c, PIN_INPUT, 0) /* (P24) GPMC0_AD4 */

AM62X_IOPAD(0x0050, PIN_INPUT, 0) /* (P22) GPMC0_AD5 */

AM62X_IOPAD(0x0054, PIN_INPUT, 0) /* (P21) GPMC0_AD6 */

AM62X_IOPAD(0x0058, PIN_INPUT, 0) /* (R23) GPMC0_AD7 */

AM62X_IOPAD(0x0084, PIN_OUTPUT, 0) /* (L23) GPMC0_ADVn_ALE */

AM62X_IOPAD(0x0088, PIN_OUTPUT, 0) /* (L24) GPMC0_OEn_REn */

AM62X_IOPAD(0x008c, PIN_OUTPUT, 0) /* (L25) GPMC0_WEn */

AM62X_IOPAD(0x0090, PIN_OUTPUT, 0) /* (M24) GPMC0_BE0n_CLE */

AM62X_IOPAD(0x00a8, PIN_OUTPUT, 0) /* (M21) GPMC0_CSn0 */

AM62X_IOPAD(0x0098, PIN_INPUT, 0) /* (U23) GPMC0_WAIT0 */

>;

};

main_i2c1_pins_default: main-i2c1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1e8, PIN_INPUT_PULLUP, 0) /* (B17) I2C1_SCL */

AM62X_IOPAD(0x1ec, PIN_INPUT_PULLUP, 0) /* (A17) I2C1_SDA */

>;

};

main_mcan0_pins_default: main-mcan0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1dc, PIN_INPUT, 0) /* (E15) MCAN0_RX */

AM62X_IOPAD(0x1d8, PIN_OUTPUT, 0) /* (C15) MCAN0_TX */

>;

};

main_mcasp2_pins_default: main-mcasp2-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x070, PIN_INPUT, 3) /* (T24) GPMC0_AD13.MCASP2_ACLKX */

AM62X_IOPAD(0x06c, PIN_INPUT, 3) /* (T22) GPMC0_AD12.MCASP2_AFSX */

AM62X_IOPAD(0x064, PIN_OUTPUT, 3) /* (T25) GPMC0_AD10.MCASP2_AXR2 */

AM62X_IOPAD(0x068, PIN_INPUT, 3) /* (R21) GPMC0_AD11.MCASP2_AXR3 */

>;

};

main_mmc1_pins_default: main-mmc1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x23c, PIN_INPUT_PULLUP, 0) /* (A21) MMC1_CMD */

AM62X_IOPAD(0x234, PIN_INPUT_PULLDOWN, 0) /* (B22) MMC1_CLK */

AM62X_IOPAD(0x230, PIN_INPUT_PULLUP, 0) /* (A22) MMC1_DAT0 */

AM62X_IOPAD(0x22c, PIN_INPUT_PULLUP, 0) /* (B21) MMC1_DAT1 */

AM62X_IOPAD(0x228, PIN_INPUT_PULLUP, 0) /* (C21) MMC1_DAT2 */

AM62X_IOPAD(0x224, PIN_INPUT_PULLUP, 0) /* (D22) MMC1_DAT3 */

AM62X_IOPAD(0x240, PIN_INPUT_PULLUP, 0) /* (D17) MMC1_SDCD */

>;

};

main_rgmii2_pins_default: main-rgmii2-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x184, PIN_INPUT, 0) /* (AE23) RGMII2_RD0 */

AM62X_IOPAD(0x188, PIN_INPUT, 0) /* (AB20) RGMII2_RD1 */

AM62X_IOPAD(0x18c, PIN_INPUT, 0) /* (AC21) RGMII2_RD2 */

AM62X_IOPAD(0x190, PIN_INPUT, 0) /* (AE22) RGMII2_RD3 */

AM62X_IOPAD(0x180, PIN_INPUT, 0) /* (AD23) RGMII2_RXC */

AM62X_IOPAD(0x17c, PIN_INPUT, 0) /* (AD22) RGMII2_RX_CTL */

AM62X_IOPAD(0x16c, PIN_OUTPUT, 0) /* (Y18) RGMII2_TD0 */

AM62X_IOPAD(0x170, PIN_OUTPUT, 0) /* (AA18) RGMII2_TD1 */

AM62X_IOPAD(0x174, PIN_OUTPUT, 0) /* (AD21) RGMII2_TD2 */

AM62X_IOPAD(0x178, PIN_OUTPUT, 0) /* (AC20) RGMII2_TD3 */

AM62X_IOPAD(0x168, PIN_OUTPUT, 0) /* (AE21) RGMII2_TXC */

AM62X_IOPAD(0x164, PIN_OUTPUT, 0) /* (AA19) RGMII2_TX_CTL */

>;

};

main_uart0_pins_default: main-uart0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1c8, PIN_INPUT, 0) /* (D14) UART0_RXD */

AM62X_IOPAD(0x1cc, PIN_OUTPUT, 0) /* (E14) UART0_TXD */

>;

};

main_uart1_pins_default: main-uart1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x194, PIN_INPUT, 2) /* (B19) MCASP0_AXR3.UART1_CTSn */

AM62X_IOPAD(0x198, PIN_OUTPUT, 2) /* (A19) MCASP0_AXR2.UART1_RTSn */

AM62X_IOPAD(0x1ac, PIN_INPUT, 2) /* (E19) MCASP0_AFSR.UART1_RXD */

AM62X_IOPAD(0x1b0, PIN_OUTPUT, 2) /* (A20) MCASP0_ACLKR.UART1_TXD */

>;

};

main_usb1_pins_default: main-usb1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x258, PIN_OUTPUT, 0) /* (F18) USB1_DRVVBUS */

>;

};

user_leds_pins_default: user-leds-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x084, PIN_OUTPUT, 7) /* (L23) GPMC0_ADVn_ALE.GPIO0_32 */

>;

};

usb_typec_int_pins_default: usb-typec-int-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x088, PIN_INPUT, 7) /* (L24) GPMC0_OEn_REn.GPIO0_33 */

>;

};

};

&gpmc0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&gpmc0_pins_default>;

ranges = <0 0 0x00 0x51000000 0x01000000>; /* CS0 space. Min partition = 16MB */

#address-cells = <2>;

#size-cells = <1>;

nand0_0: nand@0,0 {

compatible = "ti,am64-nand";

reg = <0 0 64>; /* device IO registers */

interrupt-parent = <&gpmc0>;

interrupts = <0 IRQ_TYPE_NONE>, /* fifoevent */

<1 IRQ_TYPE_NONE>; /* termcount */

rb-gpios = <&gpmc0 0 GPIO_ACTIVE_HIGH>; /* gpmc_wait0 */

ti,nand-xfer-type = "prefetch-polled";

ti,nand-ecc-opt = "bch8"; /* BCH8: Bootrom limitation */

ti,elm-id = <&elm0>;

nand-bus-width = <8>;

gpmc,device-width = <1>;

gpmc,sync-clk-ps = <0>;

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <40>;

gpmc,cs-wr-off-ns = <40>;

gpmc,adv-on-ns = <0>;

gpmc,adv-rd-off-ns = <25>;

gpmc,adv-wr-off-ns = <25>;

gpmc,we-on-ns = <0>;

gpmc,we-off-ns = <20>;

gpmc,oe-on-ns = <3>;

gpmc,oe-off-ns = <30>;

gpmc,access-ns = <30>;

gpmc,rd-cycle-ns = <40>;

gpmc,wr-cycle-ns = <40>;

gpmc,bus-turnaround-ns = <0>;

gpmc,cycle2cycle-delay-ns = <0>;

gpmc,clk-activation-ns = <0>;

gpmc,wr-access-ns = <40>;

gpmc,wr-data-mux-bus-ns = <0>;

partitions {

compatible = "fixed-partitions";

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "NAND.tiboot3";

reg = <0x00000000 0x00200000>; /* 2M */

};

partition@200000 {

label = "NAND.tispl";

reg = <0x00200000 0x00200000>; /* 2M */

};

partition@400000 {

label = "NAND.tiboot3.backup"; /* 2M */

reg = <0x00400000 0x00200000>; /* BootROM looks at 4M */

};

partition@600000 {

label = "NAND.u-boot";

reg = <0x00600000 0x00400000>; /* 4M */

};

partition@a00000 {

label = "NAND.u-boot-env";

reg = <0x00a00000 0x00040000>; /* 256K */

};

partition@a40000 {

label = "NAND.u-boot-env.backup";

reg = <0x00a40000 0x00040000>; /* 256K */

};

partition@a80000 {

label = "NAND.file-system";

reg = <0x00a80000 0x3f580000>;

};

};

};

};

&elm0{

status = "okay";

};

&audio_refclk1 {

assigned-clock-rates = <19200000>;

};

&cpsw3g {

pinctrl-names = "default";

pinctrl-0 = <&main_rgmii1_pins_default>, <&main_rgmii2_pins_default>;

};

&cpsw_port2 {

phy-mode = "rgmii-rxid";

phy-handle = <&cpsw3g_phy3>;

};

&cpsw3g_mdio {

cpsw3g_phy3: ethernet-phy@3 {

compatible = "ethernet-phy-id2000.a231", "ethernet-phy-ieee802.3-c22";

reg = <3>;

ti,clk-output-sel = <DP83867_CLK_O_SEL_OFF>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_50_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

&dss {

pinctrl-names = "default";

pinctrl-0 = <&main_dss0_pins_default>;

};

&dss_ports {

#address-cells = <1>;

#size-cells = <0>;

/* VP2: DPI/HDMI Output */

port@1 {

reg = <1>;

dpi1_out: endpoint {

remote-endpoint = <&sii9022_in>;

};

};

};

&main_i2c1 {

pinctrl-names = "default";

pinctrl-0 = <&main_i2c1_pins_default>;

clock-frequency = <100000>;

status = "okay";

audio_codec: audio-codec@18 {

pinctrl-names = "default";

pinctrl-0 = <&audio_ext_refclk1_pins_default>;

#sound-dai-cells = <0>;

compatible = "ti,tlv320aic3007";

reg = <0x18>;

ai3x-micbias-vg = <2>;

AVDD-supply = <&vcc_3v3_sw>;

IOVDD-supply = <&vcc_3v3_sw>;

DRVDD-supply = <&vcc_3v3_sw>;

DVDD-supply = <&vcc_1v8>;

};

gpio_exp: gpio-expander@21 {

pinctrl-names = "default";

pinctrl-0 = <&gpio_exp_int_pins_default>;

compatible = "nxp,pcf8574";

reg = <0x21>;

interrupt-parent = <&main_gpio1>;

interrupts = <49 0>;

#gpio-cells = <2>;

gpio-controller;

interrupt-controller;

#interrupt-cells = <2>;

gpio-line-names = "", "GPIO1_CAN0_nEN",

"GPIO2_LED2", "GPIO3_LVDS_GPIO",

"GPIO4_BUT2", "GPIO5_LVDS_BKLT_EN",

"GPIO6_ETH1_USER_RESET", "GPIO7_AUDIO_USER_RESET";

};

sii9022: bridge-hdmi@39 {

compatible = "sil,sii9022";

reg = <0x39>;

interrupt-parent = <&main_gpio0>;

interrupts = <16 IRQ_TYPE_EDGE_FALLING>;

pinctrl-names = "default";

pinctrl-0 = <&hdmi_int_pins_default>;

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

sii9022_in: endpoint {

remote-endpoint = <&dpi1_out>;

};

};

port@1 {

reg = <1>;

sii9022_out: endpoint {

remote-endpoint = <&hdmi_connector_in>;

};

};

};

};

eeprom@51 {

compatible = "atmel,24c02";

pagesize = <16>;

reg = <0x51>;

};

typec_pd: usb-pd@22 {

compatible = "ti,tps6598x";

reg = <0x22>;

/*

* HACK: The interrupt line is permanently driven low and therefore the i2c

* interface cannot be probed.

*/

#if 0

pinctrl-names = "default";

pinctrl-0 = <&usb_typec_int_pins_default>;

interrupt-parent = <&main_gpio0>;

interrupts = <33 IRQ_TYPE_LEVEL_LOW>;

interrupt-names = "irq";

#endif

connector {

compatible = "usb-c-connector";

label = "USB-C";

self-powered;

data-role = "dual";

power-role = "sink";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

usb_con_hs: endpoint {

remote-endpoint = <&typec_hs>;

};

};

};

};

};

};

&i2c_som_rtc {

enable-level-switching-mode;

};

&main_mcan0 {

pinctrl-names = "default";

pinctrl-0 = <&main_mcan0_pins_default>;

phys = <&can_tc1>;

status = "okay";

};

&main_uart0 {

pinctrl-names = "default";

pinctrl-0 = <&main_uart0_pins_default>;

status = "okay";

};

&main_uart1 {

pinctrl-names = "default";

pinctrl-0 = <&main_uart1_pins_default>;

/* Main UART1 may be used by TIFS firmware */

status = "okay";

};

&mcasp2 {

status = "okay";

#sound-dai-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&main_mcasp2_pins_default>;

/* MCASP_IIS_MODE */

op-mode = <0>;

tdm-slots = <2>;

/* 0: INACTIVE, 1: TX, 2: RX */

serial-dir = <

0 0 1 2

0 0 0 0

0 0 0 0

0 0 0 0

>;

tx-num-evt = <32>;

rx-num-evt = <32>;

};

&sdhci1 {

vmmc-supply = <&vcc_3v3_mmc>;

vqmmc-supply = <&vddshv5_sdio>;

pinctrl-names = "default";

pinctrl-0 = <&main_mmc1_pins_default>;

ti,driver-strength-ohm = <50>;

disable-wp;

no-1-8-v;

status = "okay";

};

&usbss0 {

ti,vbus-divider;

status = "okay";

};

&usbss1 {

ti,vbus-divider;

status = "okay";

};

&usb0 {

#address-cells = <1>;

#size-cells = <0>;

usb-role-switch;

port@1 {

reg = <1>;

typec_hs: endpoint {

remote-endpoint = <&usb_con_hs>;

};

};

};

&usb1 {

dr_mode = "host";

pinctrl-names = "default";

pinctrl-0 = <&main_usb1_pins_default>;

};

I've modified the .dts file for GPMC and successfully compiled the kernel and bitbake it. Are there any additional modifications needed, or anything specific I should check to ensure everything is configured correctly? because GPMC is not enumerated.

Hello,

The subject matter expert is out of office until the end of next week. Please expect a delayed response.

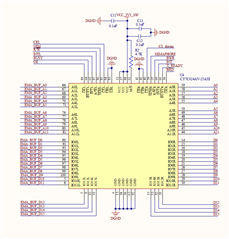

I am currently working on interfacing a CY7C024AV-25AXI SRAM with an AM625 processor. I've successfully enumerated GPMC, but I need some guidance on the following:

Supported Modes for GPMC0: Which mode supports interfacing a 4MB SRAM using CS2 on GPMC0?

Device Tree Configuration: Can anyone provide a reference .dts file or configuration snippet for setting up GPMC0 with a 4MB SRAM like the CY7C024AV-25AXI?

For your reference, I have attached the datasheet for the CY7C024AV-25AXI SRAM.CY7C026AV-25AXC-Cypress-Semiconductor.pdf

Hi Shrikant,

I am unable to provide the device tree config for the SRAM device you referred. Please refer to the kernel device tree binding files I listed above, the AM62x TRM GPMC chapter, and the SRAM device datasheet, to understand how to configure the GPMC CONFIG registers for the device.

gpmc error :

root@phyboard-lyra-am62xx-3:~# dmesg | grep gpmc

[ 1.058474] omap-gpmc 3b000000.memory-controller: GPMC revision 6.0

[ 1.064928] gpmc_mem_init: disabling cs 0 mapped at 0x0-0x1000000

[ 1.072644] omap-gpmc 3b000000.memory-controller: /bus@f0000/memory-controller@3b000000/sram@51000000 has malformed 'reg' property

[ 1.084718] omap-gpmc 3b000000.memory-controller: failed to probe DT child 'sram': -19

following .dts is using

// SPDX-License-Identifier: GPL-2.0

/*

* Copyright (C) 2022 - 2023 PHYTEC Messtechnik GmbH

* Author: Wadim Egorov <w.egorov@phytec.de>

*

* Product homepage:

* https://www.phytec.com/product/phyboard-am62x

*/

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/input/input.h>

#include <dt-bindings/leds/common.h>

#include <dt-bindings/net/ti-dp83867.h>

#include "k3-am625.dtsi"

#include "k3-am62-phycore-som.dtsi"

/ {

compatible = "phytec,am625-phyboard-lyra-rdk",

"phytec,am62-phycore-som", "ti,am625";

model = "PHYTEC phyBOARD-Lyra AM625";

aliases {

serial2 = &main_uart0;

serial3 = &main_uart1;

mmc1 = &sdhci1;

usb0 = &usb0;

usb1 = &usb1;

ethernet1 = &cpsw_port2;

};

can_tc1: can-phy0 {

compatible = "ti,tcan1042";

#phy-cells = <0>;

max-bitrate = <8000000>;

standby-gpios = <&gpio_exp 1 GPIO_ACTIVE_HIGH>;

};

hdmi0: connector-hdmi {

compatible = "hdmi-connector";

label = "hdmi";

type = "a";

port {

hdmi_connector_in: endpoint {

remote-endpoint = <&sii9022_out>;

};

};

};

keys {

compatible = "gpio-keys";

autorepeat;

pinctrl-names = "default";

pinctrl-0 = <&gpio_keys_pins_default>;

key-home {

label = "home";

linux,code = <KEY_HOME>;

gpios = <&main_gpio1 23 GPIO_ACTIVE_HIGH>;

};

key-menu {

label = "menu";

linux,code = <KEY_MENU>;

gpios = <&gpio_exp 4 GPIO_ACTIVE_HIGH>;

};

};

codec_audio: sound {

compatible = "simple-audio-card";

simple-audio-card,name = "phyBOARD-Lyra";

simple-audio-card,widgets =

"Microphone", "Mic Jack",

"Headphone", "Headphone Jack",

"Speaker", "External Speaker";

simple-audio-card,routing =

"MIC3R", "Mic Jack",

"Mic Jack", "Mic Bias",

"Headphone Jack", "HPLOUT",

"Headphone Jack", "HPROUT",

"External Speaker", "SPOP",

"External Speaker", "SPOM";

simple-audio-card,format = "dsp_b";

simple-audio-card,bitclock-master = <&sound_master>;

simple-audio-card,frame-master = <&sound_master>;

simple-audio-card,bitclock-inversion;

simple-audio-card,cpu {

sound-dai = <&mcasp2>;

};

sound_master: simple-audio-card,codec {

sound-dai = <&audio_codec>;

clocks = <&audio_refclk1>;

system-clock-frequency = <19200000>;

};

};

leds {

compatible = "gpio-leds";

pinctrl-names = "default";

pinctrl-0 = <&leds_pins_default>, <&user_leds_pins_default>;

led-1 {

gpios = <&main_gpio0 32 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "mmc0";

};

led-2 {

gpios = <&gpio_exp 2 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "mmc1";

};

};

vcc_1v8: regulator-vcc-1v8 {

compatible = "regulator-fixed";

regulator-name = "VCC_1V8";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

regulator-always-on;

regulator-boot-on;

};

vcc_3v3_mmc: regulator-vcc-3v3-mmc {

compatible = "regulator-fixed";

regulator-name = "VCC_3V3_MMC";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

regulator-boot-on;

};

vcc_3v3_sw: regulator-vcc-3v3-sw {

compatible = "regulator-fixed";

regulator-name = "VCC_3V3_SW";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

regulator-boot-on;

};

};

&main_pmx0 {

audio_ext_refclk1_pins_default: audio-ext-refclk1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x0a0, PIN_OUTPUT, 1) /* (K25) GPMC0_WPn.AUDIO_EXT_REFCLK1 */

>;

};

gpio_keys_pins_default: gpio-keys-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1d4, PIN_INPUT, 7) /* (B15) UART0_RTSn.GPIO1_23 */

>;

};

hdmi_int_pins_default: hdmi-int-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x040, PIN_INPUT, 7) /* (N23) GPMC0_AD1.GPIO0_16 */

>;

};

gpio_exp_int_pins_default: gpio-exp-int-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x244, PIN_INPUT, 7) /* (C17) MMC1_SDWP.GPIO1_49 */

>;

};

main_dss0_pins_default: main-dss0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x0b8, PIN_OUTPUT, 0) /* (U22) VOUT0_DATA0 */

AM62X_IOPAD(0x0bc, PIN_OUTPUT, 0) /* (V24) VOUT0_DATA1 */

AM62X_IOPAD(0x0e0, PIN_OUTPUT, 0) /* (V20) VOUT0_DATA10 */

AM62X_IOPAD(0x0e4, PIN_OUTPUT, 0) /* (AA23) VOUT0_DATA11 */

AM62X_IOPAD(0x0e8, PIN_OUTPUT, 0) /* (AB25) VOUT0_DATA12 */

AM62X_IOPAD(0x0ec, PIN_OUTPUT, 0) /* (AA24) VOUT0_DATA13 */

AM62X_IOPAD(0x0f0, PIN_OUTPUT, 0) /* (Y22) VOUT0_DATA14 */

AM62X_IOPAD(0x0f4, PIN_OUTPUT, 0) /* (AA21) VOUT0_DATA15 */

AM62X_IOPAD(0x0c0, PIN_OUTPUT, 0) /* (W25) VOUT0_DATA2 */

AM62X_IOPAD(0x0c4, PIN_OUTPUT, 0) /* (W24) VOUT0_DATA3 */

AM62X_IOPAD(0x0c8, PIN_OUTPUT, 0) /* (Y25) VOUT0_DATA4 */

AM62X_IOPAD(0x0cc, PIN_OUTPUT, 0) /* (Y24) VOUT0_DATA5 */

AM62X_IOPAD(0x0d0, PIN_OUTPUT, 0) /* (Y23) VOUT0_DATA6 */

AM62X_IOPAD(0x0d4, PIN_OUTPUT, 0) /* (AA25) VOUT0_DATA7 */

AM62X_IOPAD(0x0d8, PIN_OUTPUT, 0) /* (V21) VOUT0_DATA8 */

AM62X_IOPAD(0x0dc, PIN_OUTPUT, 0) /* (W21) VOUT0_DATA9 */

AM62X_IOPAD(0x0fc, PIN_OUTPUT, 0) /* (Y20) VOUT0_DE */

AM62X_IOPAD(0x0f8, PIN_OUTPUT, 0) /* (AB24) VOUT0_HSYNC */

AM62X_IOPAD(0x104, PIN_OUTPUT, 0) /* (AC24) VOUT0_PCLK */

AM62X_IOPAD(0x100, PIN_OUTPUT, 0) /* (AC25) VOUT0_VSYNC */

>;

};

/* changes by shrikant */

gpmc0_pins_default: gpmc0-pins-default {

pinctrl-single,pins = <

AM64X_IOPAD(0x0094, PIN_INPUT, 7) /* (T19) GPMC0_BE1n.GPIO0_36 */

AM64X_IOPAD(0x003c, PIN_INPUT, 0) /* (T20) GPMC0_AD0 */

AM64X_IOPAD(0x0040, PIN_INPUT, 0) /* (U21) GPMC0_AD1 */

AM64X_IOPAD(0x0064, PIN_INPUT, 0) /* (R16) GPMC0_AD10 */

AM64X_IOPAD(0x0068, PIN_INPUT, 0) /* (W20) GPMC0_AD11 */

AM64X_IOPAD(0x006c, PIN_INPUT, 0) /* (W21) GPMC0_AD12 */

AM64X_IOPAD(0x0070, PIN_INPUT, 0) /* (V18) GPMC0_AD13 */

AM64X_IOPAD(0x0074, PIN_INPUT, 0) /* (Y21) GPMC0_AD14 */

AM64X_IOPAD(0x0078, PIN_INPUT, 0) /* (Y20) GPMC0_AD15 */

AM64X_IOPAD(0x0044, PIN_INPUT, 0) /* (T18) GPMC0_AD2 */

AM64X_IOPAD(0x0048, PIN_INPUT, 0) /* (U20) GPMC0_AD3 */

AM64X_IOPAD(0x004c, PIN_INPUT, 0) /* (U18) GPMC0_AD4 */

AM64X_IOPAD(0x0050, PIN_INPUT, 0) /* (U19) GPMC0_AD5 */

AM64X_IOPAD(0x0054, PIN_INPUT, 0) /* (V20) GPMC0_AD6 */

AM64X_IOPAD(0x0058, PIN_INPUT, 0) /* (V21) GPMC0_AD7 */

AM64X_IOPAD(0x005c, PIN_INPUT, 0) /* (V19) GPMC0_AD8 */

AM64X_IOPAD(0x0060, PIN_INPUT, 0) /* (T17) GPMC0_AD9 */

AM64X_IOPAD(0x0098, PIN_INPUT_PULLUP, 0) /* (W19) GPMC0_WAIT0 */

AM64X_IOPAD(0x009c, PIN_INPUT_PULLUP, 0) /* (Y18) GPMC0_WAIT1 */

AM64X_IOPAD(0x00a8, PIN_OUTPUT_PULLUP, 0) /* (R19) GPMC0_CSn0 */

AM64X_IOPAD(0x00ac, PIN_OUTPUT_PULLUP, 0) /* (R20) GPMC0_CSn1 */

AM64X_IOPAD(0x00b0, PIN_OUTPUT_PULLUP, 0) /* (P19) GPMC0_CSn2 */

AM64X_IOPAD(0x00b4, PIN_OUTPUT_PULLUP, 0) /* (R21) GPMC0_CSn3 */

AM64X_IOPAD(0x007c, PIN_OUTPUT, 0) /* (R17) GPMC0_CLK */

AM64X_IOPAD(0x0084, PIN_OUTPUT, 0) /* (P16) GPMC0_ADVn_ALE */

AM64X_IOPAD(0x0088, PIN_OUTPUT, 0) /* (R18) GPMC0_OEn_REn */

AM64X_IOPAD(0x008c, PIN_OUTPUT, 0) /* (T21) GPMC0_WEn */

AM64X_IOPAD(0x0090, PIN_OUTPUT, 0) /* (P17) GPMC0_BE0n_CLE */

AM64X_IOPAD(0x00a0, PIN_OUTPUT_PULLUP, 0) /* (N16) GPMC0_WPn */

AM64X_IOPAD(0x00a4, PIN_OUTPUT, 0) /* (N17) GPMC0_DIR */

>;

};

/* changes by shrikant */

main_i2c1_pins_default: main-i2c1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1e8, PIN_INPUT_PULLUP, 0) /* (B17) I2C1_SCL */

AM62X_IOPAD(0x1ec, PIN_INPUT_PULLUP, 0) /* (A17) I2C1_SDA */

>;

};

main_mcan0_pins_default: main-mcan0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1dc, PIN_INPUT, 0) /* (E15) MCAN0_RX */

AM62X_IOPAD(0x1d8, PIN_OUTPUT, 0) /* (C15) MCAN0_TX */

>;

};

main_mcasp2_pins_default: main-mcasp2-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x070, PIN_INPUT, 3) /* (T24) GPMC0_AD13.MCASP2_ACLKX */

AM62X_IOPAD(0x06c, PIN_INPUT, 3) /* (T22) GPMC0_AD12.MCASP2_AFSX */

AM62X_IOPAD(0x064, PIN_OUTPUT, 3) /* (T25) GPMC0_AD10.MCASP2_AXR2 */

AM62X_IOPAD(0x068, PIN_INPUT, 3) /* (R21) GPMC0_AD11.MCASP2_AXR3 */

>;

};

main_mmc1_pins_default: main-mmc1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x23c, PIN_INPUT_PULLUP, 0) /* (A21) MMC1_CMD */

AM62X_IOPAD(0x234, PIN_INPUT_PULLDOWN, 0) /* (B22) MMC1_CLK */

AM62X_IOPAD(0x230, PIN_INPUT_PULLUP, 0) /* (A22) MMC1_DAT0 */

AM62X_IOPAD(0x22c, PIN_INPUT_PULLUP, 0) /* (B21) MMC1_DAT1 */

AM62X_IOPAD(0x228, PIN_INPUT_PULLUP, 0) /* (C21) MMC1_DAT2 */

AM62X_IOPAD(0x224, PIN_INPUT_PULLUP, 0) /* (D22) MMC1_DAT3 */

AM62X_IOPAD(0x240, PIN_INPUT_PULLUP, 0) /* (D17) MMC1_SDCD */

>;

};

main_rgmii2_pins_default: main-rgmii2-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x184, PIN_INPUT, 0) /* (AE23) RGMII2_RD0 */

AM62X_IOPAD(0x188, PIN_INPUT, 0) /* (AB20) RGMII2_RD1 */

AM62X_IOPAD(0x18c, PIN_INPUT, 0) /* (AC21) RGMII2_RD2 */

AM62X_IOPAD(0x190, PIN_INPUT, 0) /* (AE22) RGMII2_RD3 */

AM62X_IOPAD(0x180, PIN_INPUT, 0) /* (AD23) RGMII2_RXC */

AM62X_IOPAD(0x17c, PIN_INPUT, 0) /* (AD22) RGMII2_RX_CTL */

AM62X_IOPAD(0x16c, PIN_OUTPUT, 0) /* (Y18) RGMII2_TD0 */

AM62X_IOPAD(0x170, PIN_OUTPUT, 0) /* (AA18) RGMII2_TD1 */

AM62X_IOPAD(0x174, PIN_OUTPUT, 0) /* (AD21) RGMII2_TD2 */

AM62X_IOPAD(0x178, PIN_OUTPUT, 0) /* (AC20) RGMII2_TD3 */

AM62X_IOPAD(0x168, PIN_OUTPUT, 0) /* (AE21) RGMII2_TXC */

AM62X_IOPAD(0x164, PIN_OUTPUT, 0) /* (AA19) RGMII2_TX_CTL */

>;

};

main_uart0_pins_default: main-uart0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x1c8, PIN_INPUT, 0) /* (D14) UART0_RXD */

AM62X_IOPAD(0x1cc, PIN_OUTPUT, 0) /* (E14) UART0_TXD */

>;

};

main_uart1_pins_default: main-uart1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x194, PIN_INPUT, 2) /* (B19) MCASP0_AXR3.UART1_CTSn */

AM62X_IOPAD(0x198, PIN_OUTPUT, 2) /* (A19) MCASP0_AXR2.UART1_RTSn */

AM62X_IOPAD(0x1ac, PIN_INPUT, 2) /* (E19) MCASP0_AFSR.UART1_RXD */

AM62X_IOPAD(0x1b0, PIN_OUTPUT, 2) /* (A20) MCASP0_ACLKR.UART1_TXD */

>;

};

main_usb1_pins_default: main-usb1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x258, PIN_OUTPUT, 0) /* (F18) USB1_DRVVBUS */

>;

};

user_leds_pins_default: user-leds-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x084, PIN_OUTPUT, 7) /* (L23) GPMC0_ADVn_ALE.GPIO0_32 */

>;

};

usb_typec_int_pins_default: usb-typec-int-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x088, PIN_INPUT, 7) /* (L24) GPMC0_OEn_REn.GPIO0_33 */

>;

};

};

/* changes by shrikant */

&gpmc0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&gpmc0_pins_default>;

ranges = <0 0 0x00 0x51000000 0x01000000>; /* CS0 space. Min partition = 16MB */

#address-cells = <2>;

#size-cells = <1>;

nand@0,0 {

compatible = "ti,am64-nand";

reg = <0 0 64>; /* device IO registers */

interrupt-parent = <&gpmc0>;

interrupts = <0 IRQ_TYPE_NONE>, /* fifoevent */

<1 IRQ_TYPE_NONE>; /* termcount */

rb-gpios = <&gpmc0 0 GPIO_ACTIVE_HIGH>; /* gpmc_wait0 */

ti,nand-xfer-type = "prefetch-polled";

ti,nand-ecc-opt = "bch8"; /* BCH8: Bootrom limitation */

ti,elm-id = <&elm0>;

nand-bus-width = <8>;

gpmc,device-width = <1>;

gpmc,sync-clk-ps = <0>;

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <40>;

gpmc,cs-wr-off-ns = <40>;

gpmc,adv-on-ns = <0>;

gpmc,adv-rd-off-ns = <25>;

gpmc,adv-wr-off-ns = <25>;

gpmc,we-on-ns = <0>;

gpmc,we-off-ns = <20>;

gpmc,oe-on-ns = <3>;

gpmc,oe-off-ns = <30>;

gpmc,access-ns = <30>;

gpmc,rd-cycle-ns = <40>;

gpmc,wr-cycle-ns = <40>;

gpmc,bus-turnaround-ns = <0>;

gpmc,cycle2cycle-delay-ns = <0>;

gpmc,clk-activation-ns = <0>;

gpmc,wr-access-ns = <40>;

gpmc,wr-data-mux-bus-ns = <0>;

partitions {

compatible = "fixed-partitions";

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "NAND.tiboot3";

reg = <0x00000000 0x00200000>; /* 2M */

};

partition@200000 {

label = "NAND.tispl";

reg = <0x00200000 0x00200000>; /* 2M */

};

partition@400000 {

label = "NAND.tiboot3.backup"; /* 2M */

reg = <0x00400000 0x00200000>; /* BootROM looks at 4M */

};

partition@600000 {

label = "NAND.u-boot";

reg = <0x00600000 0x00400000>; /* 4M */

};

partition@a00000 {

label = "NAND.u-boot-env";

reg = <0x00a00000 0x00040000>; /* 256K */

};

partition@a40000 {

label = "NAND.u-boot-env.backup";

reg = <0x00a40000 0x00040000>; /* 256K */

};

partition@a80000 {

label = "NAND.file-system";

reg = <0x00a80000 0x3f580000>;

};

};

};

sram@51000000 {

compatible = "ti,fram";

reg = <0x51000000 0x40000>; /* Address and size of the SRAM */

#address-cells = <1>;

#size-cells = <1>;

nand-bus-width = <16>;

gpmc,device-width = <2>; /* 16-bit wide */

gpmc,sync-clk-ps = <0>;

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <85>;

gpmc,cs-wr-off-ns = <90>;

gpmc,adv-on-ns = <0>;

gpmc,adv-rd-off-ns = <10>;

gpmc,adv-wr-off-ns = <10>;

gpmc,we-on-ns = <20>;

gpmc,we-off-ns = <60>;

gpmc,oe-on-ns = <20>;

gpmc,oe-off-ns = <60>;

gpmc,access-ns = <75>; /* Max 75ns */

gpmc,rd-cycle-ns = <90>; /* Min 75ns, Max 90ns */

gpmc,wr-cycle-ns = <90>; /* Min 65ns */

gpmc,bus-turnaround-ns = <0>;

gpmc,cycle2cycle-delay-ns = <30>;

gpmc,clk-activation-ns = <0>;

gpmc,wr-access-ns = <40>;

gpmc,wr-data-mux-bus-ns = <0>;

};

};

&elm0{

status = "okay";

};

/* changes by shrikant */

&audio_refclk1 {

assigned-clock-rates = <19200000>;

};

&cpsw3g {

pinctrl-names = "default";

pinctrl-0 = <&main_rgmii1_pins_default>, <&main_rgmii2_pins_default>;

};

&cpsw_port2 {

phy-mode = "rgmii-rxid";

phy-handle = <&cpsw3g_phy3>;

};

&cpsw3g_mdio {

cpsw3g_phy3: ethernet-phy@3 {

compatible = "ethernet-phy-id2000.a231", "ethernet-phy-ieee802.3-c22";

reg = <3>;

ti,clk-output-sel = <DP83867_CLK_O_SEL_OFF>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_50_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

&dss {

pinctrl-names = "default";

pinctrl-0 = <&main_dss0_pins_default>;

};

&dss_ports {

#address-cells = <1>;

#size-cells = <0>;

/* VP2: DPI/HDMI Output */

port@1 {

reg = <1>;

dpi1_out: endpoint {

remote-endpoint = <&sii9022_in>;

};

};

};

&main_i2c1 {

pinctrl-names = "default";

pinctrl-0 = <&main_i2c1_pins_default>;

clock-frequency = <100000>;

status = "okay";

audio_codec: audio-codec@18 {

pinctrl-names = "default";

pinctrl-0 = <&audio_ext_refclk1_pins_default>;

#sound-dai-cells = <0>;

compatible = "ti,tlv320aic3007";

reg = <0x18>;

ai3x-micbias-vg = <2>;

AVDD-supply = <&vcc_3v3_sw>;

IOVDD-supply = <&vcc_3v3_sw>;

DRVDD-supply = <&vcc_3v3_sw>;

DVDD-supply = <&vcc_1v8>;

};

gpio_exp: gpio-expander@21 {

pinctrl-names = "default";

pinctrl-0 = <&gpio_exp_int_pins_default>;

compatible = "nxp,pcf8574";

reg = <0x21>;

interrupt-parent = <&main_gpio1>;

interrupts = <49 0>;

#gpio-cells = <2>;

gpio-controller;

interrupt-controller;

#interrupt-cells = <2>;

gpio-line-names = "", "GPIO1_CAN0_nEN",

"GPIO2_LED2", "GPIO3_LVDS_GPIO",

"GPIO4_BUT2", "GPIO5_LVDS_BKLT_EN",

"GPIO6_ETH1_USER_RESET", "GPIO7_AUDIO_USER_RESET";

};

sii9022: bridge-hdmi@39 {

compatible = "sil,sii9022";

reg = <0x39>;

interrupt-parent = <&main_gpio0>;

interrupts = <16 IRQ_TYPE_EDGE_FALLING>;

pinctrl-names = "default";

pinctrl-0 = <&hdmi_int_pins_default>;

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

sii9022_in: endpoint {

remote-endpoint = <&dpi1_out>;

};

};

port@1 {

reg = <1>;

sii9022_out: endpoint {

remote-endpoint = <&hdmi_connector_in>;

};

};

};

};

eeprom@51 {

compatible = "atmel,24c02";

pagesize = <16>;

reg = <0x51>;

};

typec_pd: usb-pd@22 {

compatible = "ti,tps6598x";

reg = <0x22>;

/*

* HACK: The interrupt line is permanently driven low and therefore the i2c

* interface cannot be probed.

*/

#if 0

pinctrl-names = "default";

pinctrl-0 = <&usb_typec_int_pins_default>;

interrupt-parent = <&main_gpio0>;

interrupts = <33 IRQ_TYPE_LEVEL_LOW>;

interrupt-names = "irq";

#endif

connector {

compatible = "usb-c-connector";

label = "USB-C";

self-powered;

data-role = "dual";

power-role = "sink";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

usb_con_hs: endpoint {

remote-endpoint = <&typec_hs>;

};

};

};

};

};

};

&i2c_som_rtc {

enable-level-switching-mode;

};

&main_mcan0 {

pinctrl-names = "default";

pinctrl-0 = <&main_mcan0_pins_default>;

phys = <&can_tc1>;

status = "okay";

};

&main_uart0 {

pinctrl-names = "default";

pinctrl-0 = <&main_uart0_pins_default>;

status = "okay";

};

&main_uart1 {

pinctrl-names = "default";

pinctrl-0 = <&main_uart1_pins_default>;

/* Main UART1 may be used by TIFS firmware */

status = "okay";

};

&mcasp2 {

status = "okay";

#sound-dai-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&main_mcasp2_pins_default>;

/* MCASP_IIS_MODE */

op-mode = <0>;

tdm-slots = <2>;

/* 0: INACTIVE, 1: TX, 2: RX */

serial-dir = <

0 0 1 2

0 0 0 0

0 0 0 0

0 0 0 0

>;

tx-num-evt = <32>;

rx-num-evt = <32>;

};

&sdhci1 {

vmmc-supply = <&vcc_3v3_mmc>;

vqmmc-supply = <&vddshv5_sdio>;

pinctrl-names = "default";

pinctrl-0 = <&main_mmc1_pins_default>;

ti,driver-strength-ohm = <50>;

disable-wp;

no-1-8-v;

status = "okay";

};

&usbss0 {

ti,vbus-divider;

status = "okay";

};

&usbss1 {

ti,vbus-divider;

status = "okay";

};

&usb0 {

#address-cells = <1>;

#size-cells = <0>;

usb-role-switch;

port@1 {

reg = <1>;

typec_hs: endpoint {

remote-endpoint = <&usb_con_hs>;

};

};

};

&usb1 {

dr_mode = "host";

pinctrl-names = "default";

pinctrl-0 = <&main_usb1_pins_default>;

};Hi Shrikant,

First of all, does your board have NAND device? If not, please remove the nand@0,0 node from &gpmc node.

sram@51000000 {

compatible = "ti,fram";

reg = <0x51000000 0x40000>; /* Address and size of the SRAM */

I don't have a board to validate this, but I believe the reg property here should be the same as that in your nand@0,0 node:

reg = <0 0 64>;

thanks for support. GPMC log:

root@phyboard-lyra-am62xx-3:~# dmesg | grep -i gpmc [ 1.058004] omap-gpmc 3b000000.memory-controller: GPMC revision 6.0 [ 1.064464] gpmc_mem_init: disabling cs 0 mapped at 0x0-0x1000000 root@phyboard-lyra-am62xx-3:~# devmem2 0x51000000 w 0x12345678 /dev/mem opened. Memory mapped at address 0xffff8558b000. Read at address 0x51000000 (0xffff8558b000): 0xFF4FFF4F Write at address 0x51000000 (0xffff8558b000): 0x12345678, readback 0x12345678 root@phyboard-lyra-am62xx-3:~# devmem2 0x51000000 /dev/mem opened. Memory mapped at address 0xffff8594f000. Read at address 0x51000000 (0xffff8594f000): 0x12271225

currently SRAM is not connected to Board.

The log shows writing 0x12345678 to GPMC DATA address 0x51000000, and reading it back as 0x12271225.

I think it is expected since the SRAM device is not connected to GPMC.

Please let me know if you have any other questions.