Tool/software:

Hi

I am working on the DM core of the AM62A, and I am trying to setup an interrupt for GPIO37, which is owned by the main core. I am having trouble setting up this pin IRQ to fire.

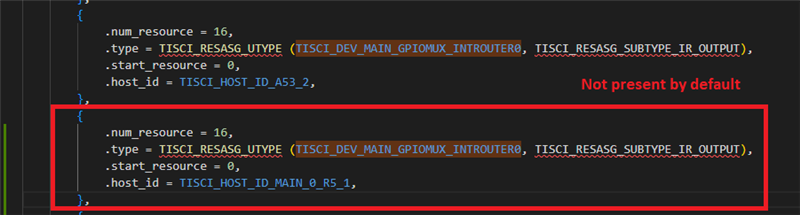

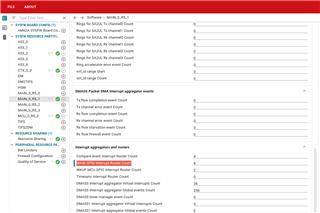

This IO (GPIO37) is on bank 2, and there is no defined BANK2 interrupt for the DM R5 core (only bank0 and bank1). So what I am trying to do instead is map the interrupt via interrupt router using the definitions found here: https://software-dl.ti.com/tisci/esd/09_02_07/5_soc_doc/am62ax/interrupt_cfg.html

I have set up this pin via syscfg, but syscfg only allows me to set up the pin as input and trigger edge, but not the interrupt itself

Here is a snippet of my current code, using the DM core MCU SDK. Code in bold are values I am unsure are correct

//Map the interrupt

struct tisci_msg_rm_irq_set_req sci_irq_req;

struct tisci_msg_rm_irq_set_resp sci_irq_res;

sci_irq_req.valid_params = 0U;

sci_irq_req.valid_params |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

sci_irq_req.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

sci_irq_req.global_event = 0U;

sci_irq_req.src_id = TISCI_DEV_MAIN_GPIOMUX_INTROUTER0;

sci_irq_req.src_index = CSLR_MAIN_GPIOMUX_INTROUTER0_IN_GPIO0_GPIO_37;

sci_irq_req.dst_id = TISCI_DEV_MAIN_GPIOMUX_INTROUTER0;

sci_irq_req.dst_host_irq = 12; //Use 12, which maps to interrupt 44

sci_irq_req.ia_id = 0U;

sci_irq_req.vint = 0U;

sci_irq_req.vint_status_bit_index = 0U;

sci_irq_req.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSet(&sci_irq_req, &sci_irq_res, SystemP_WAIT_FOREVER);

if(0 != retVal)

{

DebugP_log("Error: Sciclient event config failed!\r\n");

}

//Setup GPIO

bank_num = GPIO_GET_BANK_INDEX(37);

GPIO_setDirMode(CSL_GPIO0_BASE, 37, GPIO_DIRECTION_INPUT);

GPIO_setTrigType(CSL_GPIO0_BASE, 37, GPIO_TRIG_TYPE_RISE_EDGE);

GPIO_bankIntrEnable(CSL_GPIO0_BASE, 37);

//Setup HWiP

HwiP_Params_init(&hwi_params);

hwi_params.intNum = CSLR_WKUP_R5FSS0_CORE0_INTR_MAIN_GPIOMUX_INTROUTER0_OUTP_12; ///This is chosen due to above interrupt mapping

hwi_params.eventId = HWIP_INVALID_EVENT_ID; //Not used for AM62A

hwi_params.priority = 3;

hwi_params.isFIQ = 0; //interrupt is ISR

hwi_params.isPulse = 1; //pulse interrupt

hwi_params.callback = &irq_callback;

hwi_params.args = NULL;

HwiP_construct(hwi_object, &hwi_params);

When running this code on the DM core:

1. The Sciclient_rmIrqSet function returns a non-zero error code, signalling this function has failed

2. The IRQ callback function never gets called, even though through a probe, I can see that GPIO37 is generating rising edges

Am I missing some step, or incorrectly setting up the interrupt?

Thanks!