Tool/software:

I want to enable the DSS DPI port using MCU3_0

I am using ti-processor-sdk-rtos-j721s2-evm-08_06_00_11 RTOS SDK.

My setup build is compiled with flag BUILD_EDGEAI

Linux as the main OS is running on A72 core.

DSS is disabled in Linux device tree.

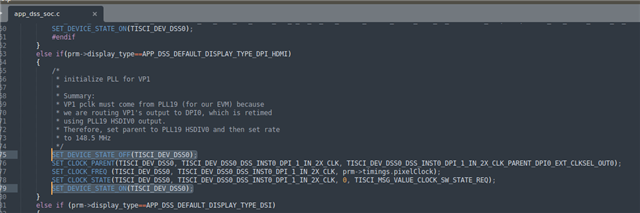

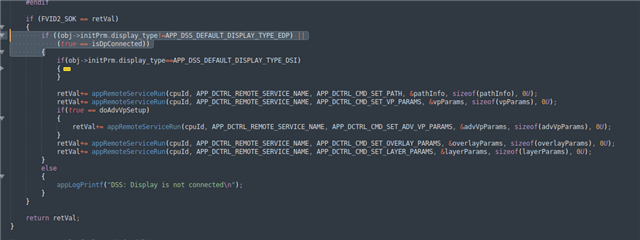

Currently, the DSS init on RTOS on MCU3_0 gets stack on DSS driver init

I added some prints to see where it is stack. And I see that it is stack here: appDssDefaultInit -> appDssInit -> Dss_init -> Dss_dctrlDrvInit

How my DSS init looks like in the main task of MCU3_0:

/*

*

* Copyright (c) 2018 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include <app.h>

#include <utils/console_io/include/app_log.h>

#include <stdio.h>

#include <string.h>

#include <ti/osal/osal.h>

#include <ti/osal/TaskP.h>

#include <app_ipc_rsctable.h>

#include <ti/csl/csl_types.h>

/* Vision_apps utils header files */

#include <utils/console_io/include/app_log.h>

#include <utils/misc/include/app_misc.h>

#include <utils/dss/include/app_dss_defaults.h>

#include <utils/sensors/include/app_sensors.h>

#include <utils/udma/include/app_udma.h>

#include <utils/hwa/include/app_hwa.h>

/* TIOVX header files */

#include <TI/tivx.h>

#define APP_ASSERT_SUCCESS(x) { if((x)!=0) while(1); }

static void initDssDPI(void);

static void appMain(void* arg0, void* arg1)

{

appInit();

appRun();

initDssDPI();

#if 1

while(1)

{

appLogPrintf("I am Alive from MCU-3 v11 :=)\n");

appLogWaitMsecs(10000u);

}

#else

deinitDssDPI();

appDeInit();

#endif

}

void StartupEmulatorWaitFxn (void)

{

volatile uint32_t enableDebug = 0;

do

{

}while (enableDebug);

}

static uint8_t gTskStackMain[8*1024]

__attribute__ ((section(".bss:taskStackSection")))

__attribute__ ((aligned(8192)))

;

int main(void)

{

TaskP_Params tskParams;

TaskP_Handle task;

/* This is for debug purpose - see the description of function header */

StartupEmulatorWaitFxn();

OS_init();

TaskP_Params_init(&tskParams);

tskParams.priority = 8u;

tskParams.stack = gTskStackMain;

tskParams.stacksize = sizeof (gTskStackMain);

task = TaskP_create(&appMain, &tskParams);

if(NULL == task)

{

OS_stop();

}

OS_start();

return 0;

}

uint32_t appGetDdrSharedHeapSize()

{

return DDR_SHARED_MEM_SIZE;

}

static void initDssDPI(void)

{

int32_t status = 0;

// ENABLE_PRINTF_REDIRECT

status = appLogCioInit();

APP_ASSERT_SUCCESS(status);

// ENABLE_UDMA

appLogPrintf("Start UDMA init\n");

status = appUdmaInit();

APP_ASSERT_SUCCESS(status);

appLogPrintf("End UDMA init\n");

appLogPrintf("Start DSS init\n");

// ENABLE_BOARD

{

app_pinmux_cfg_t pinmux_cfg;

appPinMuxCfgSetDefault(&pinmux_cfg);

pinmux_cfg.enable_i2c = TRUE; /* i2c is needed for on board HDMI mux config, eDP to HDMI adapter config */

pinmux_cfg.enable_hdmi = TRUE;

appSetPinmux(&pinmux_cfg);

}

appLogPrintf("<<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : PRE FVID2 init !!!\n");

// ENABLE_FVID2

status = appFvid2Init();

APP_ASSERT_SUCCESS(status);

appLogPrintf("<<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : AFTER FVID2 init !!!\n");

appLogPrintf("<<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : PRE I2C init !!!\n");

// ENABLE_I2C

appI2cInit();

appLogPrintf("<<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : AFTER I2C init !!!\n");

// ENABLE_DSS_SINGLE

{

app_dss_default_prm_t prm;

appDssDefaultSetDefaultPrm(&prm);

//ENABLE_DSS_HDMI

prm.display_type = APP_DSS_DEFAULT_DISPLAY_TYPE_DPI_HDMI;

prm.enableM2m = true;

/* Do not rely on "init". Always provide known good tmings */

prm.timings.width = 1920U;

prm.timings.height = 1080U;

prm.timings.hFrontPorch = 88U;

prm.timings.hBackPorch = 148U;

prm.timings.hSyncLen = 44U;

prm.timings.vFrontPorch = 4U;

prm.timings.vBackPorch = 36U;

prm.timings.vSyncLen = 5U;

prm.timings.pixelClock = 148500000ULL;

status = appDssDefaultInit(&prm);

APP_ASSERT_SUCCESS(status);

}

appLogPrintf("End DSS init\n");

tivxRegisterHwaTargetDisplayKernels();

tivxRegisterHwaTargetDisplayM2MKernels();

appLogPrintf("OpenVX DSS Target kernel init ... Done !!!\n");

}

static void deinitDssDPI(void)

{

appDssDefaultDeInit();

appI2cDeInit();

}

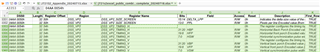

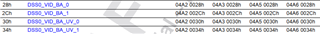

Here are the logs of the R5 cores:

root@j721s2-evm:/opt/vision_apps-v3# ./vx_app_arm_remote_log.out [MCU2_0] 23.889762 s: CIO: Init ... Done !!! [MCU2_0] 23.889813 s: ### CPU Frequency = 1000000000 Hz [MCU2_0] 23.889847 s: CPU is running FreeRTOS [MCU2_0] 23.889869 s: APP: Init ... !!! [MCU2_0] 23.889890 s: SCICLIENT: Init ... !!! [MCU2_0] 23.890004 s: SCICLIENT: DMSC FW version [9.0.6--v09.00.06 (Kool Koala)] [MCU2_0] 23.890038 s: SCICLIENT: DMSC FW revision 0x9 [MCU2_0] 23.890066 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU2_0] 23.890099 s: SCICLIENT: Init ... Done !!! [MCU2_0] 23.890122 s: UDMA: Init ... !!! [MCU2_0] 23.890890 s: UDMA: Init ... Done !!! [MCU2_0] 23.890924 s: UDMA: Init ... !!! [MCU2_0] 23.891355 s: UDMA: Init for CSITX/CSIRX ... Done !!! [MCU2_0] 23.891409 s: MEM: Init ... !!! [MCU2_0] 23.891446 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ d9000000 of size 16777216 bytes !!! [MCU2_0] 23.891506 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 60000000 of size 524288 bytes !!! [MCU2_0] 23.891561 s: MEM: Init ... Done !!! [MCU2_0] 23.891583 s: IPC: Init ... !!! [MCU2_0] 23.891632 s: IPC: 5 CPUs participating in IPC !!! [MCU2_0] 23.891667 s: IPC: Waiting for HLOS to be ready ... !!! [MCU2_0] 23.891693 s: IPC: HLOS is ready !!! [MCU2_0] 23.901201 s: IPC: Init ... Done !!! [MCU2_0] 23.901239 s: APP: Syncing with 5 CPUs ... !!! [MCU2_0] 24.333885 s: APP: Syncing with 5 CPUs ... Done !!! [MCU2_0] 24.333918 s: REMOTE_SERVICE: Init ... !!! [MCU2_0] 24.335375 s: REMOTE_SERVICE: Init ... Done !!! [MCU2_0] 24.335414 s: FVID2: Init ... !!! [MCU2_0] 24.335469 s: FVID2: Init ... Done !!! [MCU2_0] 24.335493 s: VHWA: VPAC Init ... !!! [MCU2_0] 24.335517 s: SCICLIENT: Sciclient_pmSetModuleState module=361 state=2 [MCU2_0] 24.335643 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 24.335674 s: VHWA: LDC Init ... !!! [MCU2_0] 24.338382 s: VHWA: LDC Init ... Done !!! [MCU2_0] 24.338423 s: VHWA: MSC Init ... !!! [MCU2_0] 24.348060 s: VHWA: MSC Init ... Done !!! [MCU2_0] 24.348094 s: VHWA: NF Init ... !!! [MCU2_0] 24.348949 s: VHWA: NF Init ... Done !!! [MCU2_0] 24.348978 s: VHWA: VISS Init ... !!! [MCU2_0] 24.356199 s: VHWA: VISS Init ... Done !!! [MCU2_0] 24.356240 s: VHWA: VPAC Init ... Done !!! [MCU2_0] 24.356277 s: VX_ZONE_INIT:Enabled [MCU2_0] 24.356302 s: VX_ZONE_ERROR:Enabled [MCU2_0] 24.356325 s: VX_ZONE_WARNING:Enabled [MCU2_0] 24.357324 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU2-0 [MCU2_0] 24.357515 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_NF [MCU2_0] 24.357684 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_LDC1 [MCU2_0] 24.357853 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_MSC1 [MCU2_0] 24.358023 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_MSC2 [MCU2_0] 24.358240 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_VISS1 [MCU2_0] 24.358463 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE1 [MCU2_0] 24.358663 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE2 [MCU2_0] 24.358868 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DISPLAY1 [MCU2_0] 24.359070 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DISPLAY2 [MCU2_0] 24.359255 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CSITX [MCU2_0] 24.359465 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE3 [MCU2_0] 24.359645 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE4 [MCU2_0] 24.359826 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE5 [MCU2_0] 24.360002 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE6 [MCU2_0] 24.360193 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE7 [MCU2_0] 24.360384 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE8 [MCU2_0] 24.360573 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M1 [MCU2_0] 24.360757 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M2 [MCU2_0] 24.360942 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M3 [MCU2_0] 24.361123 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M4 [MCU2_0] 24.361304 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CSITX2 [MCU2_0] 24.361348 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!! [MCU2_0] 24.361377 s: APP: OpenVX Target kernel init ... !!! [MCU2_0] 24.391661 s: APP: OpenVX Target kernel init ... Done !!! [MCU2_0] 24.391696 s: VISS REMOTE SERVICE: Init ... !!! [MCU2_0] 24.391758 s: VISS REMOTE SERVICE: Init ... Done !!! [MCU2_0] 24.391786 s: UDMA Copy: Init ... !!! [MCU2_0] 24.392624 s: UDMA Copy: Init ... Done !!! [MCU2_0] 24.392687 s: APP: Init ... Done !!! [MCU2_0] 24.392713 s: APP: Run ... !!! [MCU2_0] 24.392735 s: IPC: Starting echo test ... [MCU2_0] 24.395119 s: APP: Run ... Done !!! [MCU2_0] 24.395810 s: IPC: Echo status: mcu2_0[s] mcu2_1[.] mcu3_0[x] C7X_1[P] C7X_2[.] [MCU2_0] 24.395888 s: IPC: Echo status: mcu2_0[s] mcu2_1[P] mcu3_0[x] C7X_1[P] C7X_2[.] [MCU2_0] 24.395955 s: IPC: Echo status: mcu2_0[s] mcu2_1[P] mcu3_0[x] C7X_1[P] C7X_2[P] [MCU2_1] 24.178070 s: CIO: Init ... Done !!! [MCU2_1] 24.178120 s: ### CPU Frequency = 1000000000 Hz [MCU2_1] 24.178151 s: CPU is running FreeRTOS [MCU2_1] 24.178171 s: APP: Init ... !!! [MCU2_1] 24.178191 s: SCICLIENT: Init ... !!! [MCU2_1] 24.178308 s: SCICLIENT: DMSC FW version [9.0.6--v09.00.06 (Kool Koala)] [MCU2_1] 24.178342 s: SCICLIENT: DMSC FW revision 0x9 [MCU2_1] 24.178369 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU2_1] 24.178399 s: SCICLIENT: Init ... Done !!! [MCU2_1] 24.178422 s: UDMA: Init ... !!! [MCU2_1] 24.179228 s: UDMA: Init ... Done !!! [MCU2_1] 24.179276 s: MEM: Init ... !!! [MCU2_1] 24.179309 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ da000000 of size 16777216 bytes !!! [MCU2_1] 24.179367 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 60080000 of size 524288 bytes !!! [MCU2_1] 24.179418 s: MEM: Init ... Done !!! [MCU2_1] 24.179439 s: IPC: Init ... !!! [MCU2_1] 24.179485 s: IPC: 5 CPUs participating in IPC !!! [MCU2_1] 24.179518 s: IPC: Waiting for HLOS to be ready ... !!! [MCU2_1] 24.179544 s: IPC: HLOS is ready !!! [MCU2_1] 24.189025 s: IPC: Init ... Done !!! [MCU2_1] 24.189062 s: APP: Syncing with 5 CPUs ... !!! [MCU2_1] 24.333884 s: APP: Syncing with 5 CPUs ... Done !!! [MCU2_1] 24.333915 s: REMOTE_SERVICE: Init ... !!! [MCU2_1] 24.335230 s: REMOTE_SERVICE: Init ... Done !!! [MCU2_1] 24.335265 s: FVID2: Init ... !!! [MCU2_1] 24.335315 s: FVID2: Init ... Done !!! [MCU2_1] 24.335337 s: VHWA: DMPAC: Init ... !!! [MCU2_1] 24.335358 s: SCICLIENT: Sciclient_pmSetModuleState module=58 state=2 [MCU2_1] 24.335479 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_1] 24.335508 s: SCICLIENT: Sciclient_pmSetModuleState module=62 state=2 [MCU2_1] 24.335577 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_1] 24.335640 s: VHWA: DOF Init ... !!! [MCU2_1] 24.339819 s: VHWA: DOF Init ... Done !!! [MCU2_1] 24.339854 s: VHWA: SDE Init ... !!! [MCU2_1] 24.341388 s: VHWA: SDE Init ... Done !!! [MCU2_1] 24.341420 s: VHWA: DMPAC: Init ... Done !!! [MCU2_1] 24.341454 s: VX_ZONE_INIT:Enabled [MCU2_1] 24.341477 s: VX_ZONE_ERROR:Enabled [MCU2_1] 24.341499 s: VX_ZONE_WARNING:Enabled [MCU2_1] 24.342506 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU2-1 [MCU2_1] 24.342684 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DMPAC_SDE [MCU2_1] 24.342865 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DMPAC_DOF [MCU2_1] 24.342906 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!! [MCU2_1] 24.342934 s: APP: OpenVX Target kernel init ... !!! [MCU2_1] 24.343152 s: APP: OpenVX Target kernel init ... Done !!! [MCU2_1] 24.343180 s: UDMA Copy: Init ... !!! [MCU2_1] 24.344422 s: UDMA Copy: Init ... Done !!! [MCU2_1] 24.344462 s: APP: Init ... Done !!! [MCU2_1] 24.344488 s: APP: Run ... !!! [MCU2_1] 24.344508 s: IPC: Starting echo test ... [MCU2_1] 24.346567 s: APP: Run ... Done !!! [MCU2_1] 24.347065 s: IPC: Echo status: mcu2_0[x] mcu2_1[s] mcu3_0[x] C7X_1[P] C7X_2[.] [MCU2_1] 24.347133 s: IPC: Echo status: mcu2_0[x] mcu2_1[s] mcu3_0[x] C7X_1[P] C7X_2[P] [MCU2_1] 24.395689 s: IPC: Echo status: mcu2_0[P] mcu2_1[s] mcu3_0[x] C7X_1[P] C7X_2[P] [MCU3_0] 24.324148 s: CIO: Init ... Done !!! [MCU3_0] 24.324196 s: ### CPU Frequency = 1000000000 Hz [MCU3_0] 24.324227 s: CPU is running FreeRTOS [MCU3_0] 24.324247 s: APP: Init ... !!! [MCU3_0] 24.324266 s: SCICLIENT: Init ... !!! [MCU3_0] 24.324380 s: SCICLIENT: DMSC FW version [9.0.6--v09.00.06 (Kool Koala)] [MCU3_0] 24.324412 s: SCICLIENT: DMSC FW revision 0x9 [MCU3_0] 24.324439 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU3_0] 24.324470 s: SCICLIENT: Init ... Done !!! [MCU3_0] 24.324492 s: MEM: Init ... !!! [MCU3_0] 24.324522 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ db000000 of size 8388608 bytes !!! [MCU3_0] 24.324577 s: MEM: Init ... Done !!! [MCU3_0] 24.324599 s: IPC: Init ... !!! [MCU3_0] 24.324641 s: IPC: 5 CPUs participating in IPC !!! [MCU3_0] 24.324676 s: IPC: Waiting for HLOS to be ready ... !!! [MCU3_0] 24.324702 s: IPC: HLOS is ready !!! [MCU3_0] 24.333812 s: IPC: Init ... Done !!! [MCU3_0] 24.333849 s: APP: Syncing with 5 CPUs ... !!! [MCU3_0] 24.333884 s: APP: Syncing with 5 CPUs ... Done !!! [MCU3_0] 24.333914 s: REMOTE_SERVICE: Init ... !!! [MCU3_0] 24.335423 s: REMOTE_SERVICE: Init ... Done !!! [MCU3_0] 24.335469 s: VX_ZONE_INIT:Enabled [MCU3_0] 24.335493 s: VX_ZONE_ERROR:Enabled [MCU3_0] 24.335515 s: VX_ZONE_WARNING:Enabled [MCU3_0] 24.336463 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU3-0 [MCU3_0] 24.336507 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!! [MCU3_0] 24.336536 s: APP: OpenVX Target kernel init ... !!! [MCU3_0] 24.336561 s: APP: OpenVX Target kernel init ... Done !!! [MCU3_0] 24.336586 s: APP: Init ... Done !!! [MCU3_0] 24.336609 s: APP: Run ... !!! [MCU3_0] 24.336629 s: IPC: Starting echo test ... [MCU3_0] 24.339005 s: APP: Run ... Done !!! [MCU3_0] 24.339068 s: CIO: Init ... Done !!! [MCU3_0] 24.339095 s: Start UDMA init [MCU3_0] 24.339115 s: UDMA: Init ... !!! [MCU3_0] 24.340729 s: UDMA: Init ... Done !!! [MCU3_0] 24.340765 s: End UDMA init [MCU3_0] 24.340791 s: Start DSS init [MCU3_0] 24.340820 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : PRE FVID2 init !!! [MCU3_0] 24.340849 s: FVID2: Init ... !!! [MCU3_0] 24.340906 s: FVID2: Init ... Done !!! [MCU3_0] 24.340931 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : AFTER FVID2 init !!! [MCU3_0] 24.340960 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : PRE I2C init !!! [MCU3_0] 24.340989 s: SCICLIENT: Sciclient_pmSetModuleState module=219 state=2 [MCU3_0] 24.341090 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU3_0] 24.341129 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : AFTER I2C init !!! [MCU3_0] 24.341161 s: DSS: Init ... !!! [MCU3_0] 24.341183 s: DSS: Display type is HDMI !!! [MCU3_0] 24.341206 s: DSS: M2M Path is enabled !!! [MCU3_0] 24.341230 s: DSS: SoC init ... !!! [MCU3_0] 24.341251 s: SCICLIENT: Sciclient_pmSetModuleState module=158 state=0 [MCU3_0] 24.341312 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU3_0] 24.341341 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=158 clk=5 parent=7 [MCU3_0] 24.341415 s: SCICLIENT: Sciclient_pmSetModuleClkParent success [MCU3_0] 24.341444 s: SCICLIENT: Sciclient_pmSetModuleClkFreq module=158 clk=5 freq=148500000 [MCU3_0] 24.342463 s: SCICLIENT: Sciclient_pmSetModuleClkFreq success [MCU3_0] 24.342490 s: SCICLIENT: Sciclient_pmModuleClkRequest module=158 clk=5 state=2 flag=0 [MCU3_0] 24.342598 s: SCICLIENT: Sciclient_pmModuleClkRequest success [MCU3_0] 24.342625 s: DSS: SoC init ... Done !!! [MCU3_0] 24.342648 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : DSS: PRE conf board !!! [MCU3_0] 24.342678 s: DSS: Board init ... !!! [MCU3_0] 24.342699 s: DSS: Board init ... Done !!! [MCU3_0] 24.342721 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : DSS: AFTER conf board !!! [MCU3_0] 24.342753 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : PRE APP DSS init !!! [MCU3_0] 24.342789 s: <<<<<<<<<<<<<<<TEST>>>>>>>>>>>>>>> : DSS: PRE Dss_init !!! [MCU3_0] 24.342830 s: src/drv/common/dss_init.c @ Line 102: [MCU3_0] 24.342856 s: Before param check [MCU3_0] 24.342883 s: src/drv/common/dss_init.c @ Line 109: [MCU3_0] 24.342909 s: After param check [MCU3_0] 24.342940 s: src/drv/common/dss_init.c @ Line 116: [MCU3_0] 24.342966 s: Before EM [MCU3_0] 24.343150 s: src/drv/common/dss_init.c @ Line 123: [MCU3_0] 24.343175 s: After EM [MCU3_0] 24.343199 s: src/drv/common/dss_init.c @ Line 154: [MCU3_0] 24.343224 s: Before driver [C7x_1 ] 23.504204 s: CIO: Init ... Done !!! [C7x_1 ] 23.504219 s: ### CPU Frequency = 1000000000 Hz [C7x_1 ] 23.504231 s: CPU is running FreeRTOS [C7x_1 ] 23.504239 s: APP: Init ... !!! [C7x_1 ] 23.504247 s: SCICLIENT: Init ... !!! [C7x_1 ] 23.504341 s: SCICLIENT: DMSC FW version [9.0.6--v09.00.06 (Kool Koala)] [C7x_1 ] 23.504356 s: SCICLIENT: DMSC FW revision 0x9 [C7x_1 ] 23.504367 s: SCICLIENT: DMSC FW ABI revision 3.1 [C7x_1 ] 23.504378 s: SCICLIENT: Init ... Done !!! [C7x_1 ] 23.504387 s: UDMA: Init ... !!! [C7x_1 ] 23.505083 s: UDMA: Init ... Done !!! [C7x_1 ] 23.505095 s: MEM: Init ... !!! [C7x_1 ] 23.505112 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 117000000 of size 268435456 bytes !!! [C7x_1 ] 23.505134 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 70020000 of size 3964928 bytes !!! [C7x_1 ] 23.505152 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 64800000 of size 458752 bytes !!! [C7x_1 ] 23.505170 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 64e00000 of size 16384 bytes !!! [C7x_1 ] 23.505187 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 100000000 of size 385875968 bytes !!! [C7x_1 ] 23.505206 s: MEM: Init ... Done !!! [C7x_1 ] 23.505214 s: IPC: Init ... !!! [C7x_1 ] 23.505228 s: IPC: 5 CPUs participating in IPC !!! [C7x_1 ] 23.505243 s: IPC: Waiting for HLOS to be ready ... !!! [C7x_1 ] 23.505254 s: IPC: HLOS is ready !!! [C7x_1 ] 23.506861 s: IPC: Init ... Done !!! [C7x_1 ] 23.506874 s: APP: Syncing with 5 CPUs ... !!! [C7x_1 ] 24.333886 s: APP: Syncing with 5 CPUs ... Done !!! [C7x_1 ] 24.333903 s: REMOTE_SERVICE: Init ... !!! [C7x_1 ] 24.334040 s: REMOTE_SERVICE: Init ... Done !!! [C7x_1 ] 24.334063 s: VX_ZONE_INIT:Enabled [C7x_1 ] 24.334101 s: VX_ZONE_ERROR:Enabled [C7x_1 ] 24.334113 s: VX_ZONE_WARNING:Enabled [C7x_1 ] 24.334334 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1 [C7x_1 ] 24.334396 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_2 [C7x_1 ] 24.334456 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_3 [C7x_1 ] 24.334517 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_4 [C7x_1 ] 24.334576 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_5 [C7x_1 ] 24.334635 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_6 [C7x_1 ] 24.334693 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_7 [C7x_1 ] 24.334753 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_8 [C7x_1 ] 24.334778 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!! [C7x_1 ] 24.334791 s: APP: OpenVX Target kernel init ... !!! [C7x_1 ] 24.334920 s: APP: OpenVX Target kernel init ... Done !!! [C7x_1 ] 24.334932 s: APP: Init ... Done !!! [C7x_1 ] 24.334941 s: APP: Run ... !!! [C7x_1 ] 24.334950 s: IPC: Starting echo test ... [C7x_1 ] 24.335063 s: APP: Run ... Done !!! [C7x_1 ] 24.335817 s: IPC: Echo status: mcu2_0[x] mcu2_1[x] mcu3_0[x] C7X_1[s] C7X_2[P] [C7x_1 ] 24.346976 s: IPC: Echo status: mcu2_0[x] mcu2_1[P] mcu3_0[x] C7X_1[s] C7X_2[P] [C7x_1 ] 24.395700 s: IPC: Echo status: mcu2_0[P] mcu2_1[P] mcu3_0[x] C7X_1[s] C7X_2[P] [C7x_2 ] 23.489078 s: CIO: Init ... Done !!! [C7x_2 ] 23.489093 s: ### CPU Frequency = 1000000000 Hz [C7x_2 ] 23.489105 s: CPU is running FreeRTOS [C7x_2 ] 23.489113 s: APP: Init ... !!! [C7x_2 ] 23.489122 s: SCICLIENT: Init ... !!! [C7x_2 ] 23.489218 s: SCICLIENT: DMSC FW version [9.0.6--v09.00.06 (Kool Koala)] [C7x_2 ] 23.489233 s: SCICLIENT: DMSC FW revision 0x9 [C7x_2 ] 23.489244 s: SCICLIENT: DMSC FW ABI revision 3.1 [C7x_2 ] 23.489255 s: SCICLIENT: Init ... Done !!! [C7x_2 ] 23.489264 s: UDMA: Init ... !!! [C7x_2 ] 23.490030 s: UDMA: Init ... Done !!! [C7x_2 ] 23.490043 s: MEM: Init ... !!! [C7x_2 ] 23.490053 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 127000000 of size 16777216 bytes !!! [C7x_2 ] 23.490074 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 65800000 of size 458752 bytes !!! [C7x_2 ] 23.490092 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 65e00000 of size 16384 bytes !!! [C7x_2 ] 23.490110 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 128000000 of size 67108864 bytes !!! [C7x_2 ] 23.490129 s: MEM: Init ... Done !!! [C7x_2 ] 23.490137 s: IPC: Init ... !!! [C7x_2 ] 23.490150 s: IPC: 5 CPUs participating in IPC !!! [C7x_2 ] 23.490164 s: IPC: Waiting for HLOS to be ready ... !!! [C7x_2 ] 23.490176 s: IPC: HLOS is ready !!! [C7x_2 ] 23.491699 s: IPC: Init ... Done !!! [C7x_2 ] 23.491713 s: APP: Syncing with 5 CPUs ... !!! [C7x_2 ] 24.333886 s: APP: Syncing with 5 CPUs ... Done !!! [C7x_2 ] 24.333905 s: REMOTE_SERVICE: Init ... !!! [C7x_2 ] 24.334045 s: REMOTE_SERVICE: Init ... Done !!! [C7x_2 ] 24.334071 s: VX_ZONE_INIT:Enabled [C7x_2 ] 24.334109 s: VX_ZONE_ERROR:Enabled [C7x_2 ] 24.334122 s: VX_ZONE_WARNING:Enabled [C7x_2 ] 24.334596 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP-1 [C7x_2 ] 24.334619 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!! [C7x_2 ] 24.334632 s: APP: OpenVX Target kernel init ... !!! [C7x_2 ] 24.334878 s: APP: OpenVX Target kernel init ... Done !!! [C7x_2 ] 24.334894 s: UDMA Copy: Init ... !!! [C7x_2 ] 24.335420 s: UDMA Copy: Init ... Done !!! [C7x_2 ] 24.335434 s: APP: Init ... Done !!! [C7x_2 ] 24.335445 s: APP: Run ... !!! [C7x_2 ] 24.335454 s: IPC: Starting echo test ... [C7x_2 ] 24.335564 s: APP: Run ... Done !!! [C7x_2 ] 24.335824 s: IPC: Echo status: mcu2_0[x] mcu2_1[x] mcu3_0[x] C7X_1[P] C7X_2[s] [C7x_2 ] 24.347046 s: IPC: Echo status: mcu2_0[x] mcu2_1[P] mcu3_0[x] C7X_1[P] C7X_2[s] [C7x_2 ] 24.395714 s: IPC: Echo status: mcu2_0[P] mcu2_1[P] mcu3_0[x] C7X_1[P] C7X_2[s]

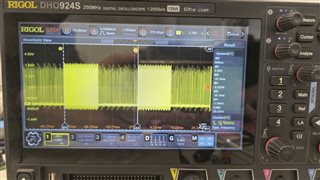

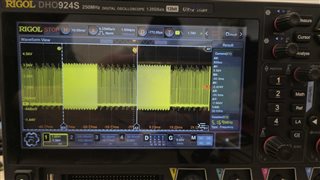

Please help me to setup DSS on MCU3_0