Tool/software:

hello teams:

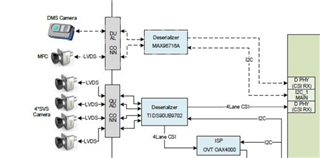

we are developing mfc camera driver in our project, the partial hardware architecture is as follows:

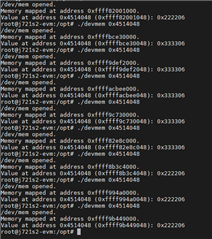

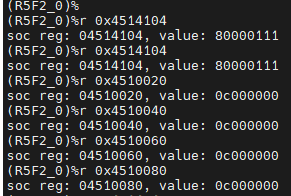

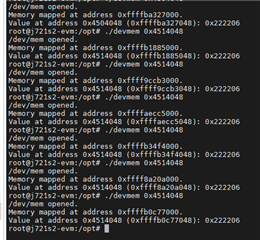

the circumstances is that we have measured data lane and clock lane by oscilloscope from MAX96716,whose waveform is in line with expectations. but when we read CSI_RX_IF_VBUS2APB_DPHY_STATUS register

by devmem2,the value is always 0x222206. from your doc,the register value should vary between 0x333306 and 0x222206.

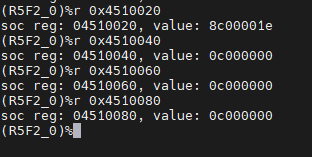

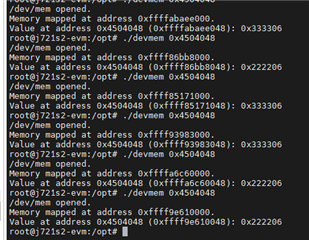

when we connected svs camera which can produce a normal camera image, the register value is as follows.

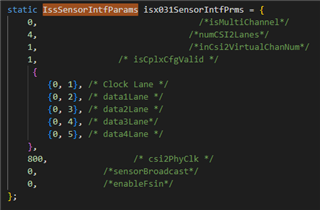

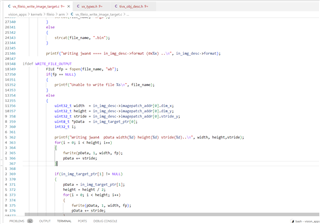

and our video pipeline can't receive camera data from mfc camera. it might be video pipeline has a wrong parameter setting or there is something wrong with csirx driver.

what i want to ask is , is there something wrong with csirx , or the wrong video pipeline parameter might cause abnormal register value in csirx module?