Tool/software:

Hi,

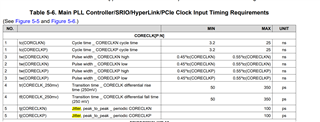

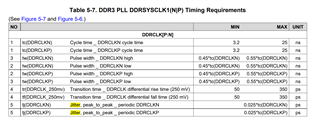

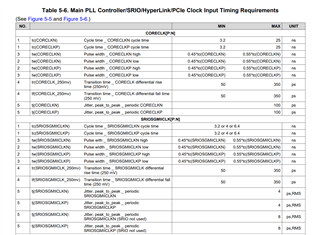

In the data sheet for jitter measurements, the specs are in peak-to-peak and RMS. I measured the core clock and DDR clock so not sure what BER to select to go from peak-to-peak to RMS. What is the factor I should use to go from peak-to-peak to RMS as my measurements are in RMS? What value is being used for the BER to go to RMS?

Thanks,

Luke