Tool/software:

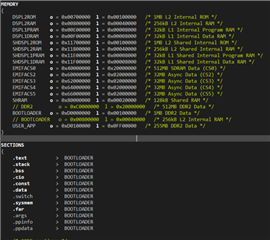

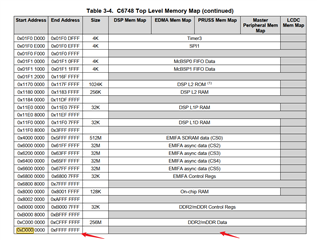

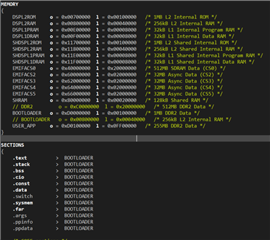

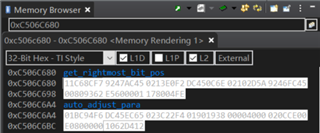

After reading Chapter 3.4 of the Memory Map Summary of the manual "TMS320C6748 Fixed- and Floating-Point DSP datasheet (Rev. G).pdf, there are some undefined memory, such as 0xD000 000 - 0xFFFF FFF, in fact, it is normal to read and write to the address behind the 0xD0000000 inside the program. I feel like it's working for 0xD0000000, and I'd like to confirm how this undefined memory segment is used.