Tool/software:

While configuring LPSCs of A72 (PDs are already turned ON) to power OFF, we faced a unknown status in the LPSC status register, which does not allow to turn the LPSC back ON.

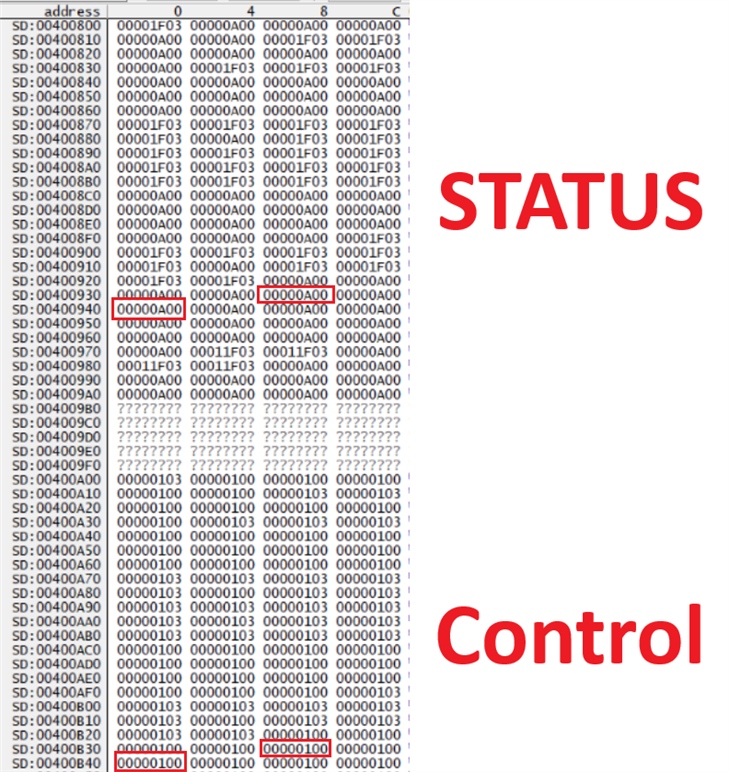

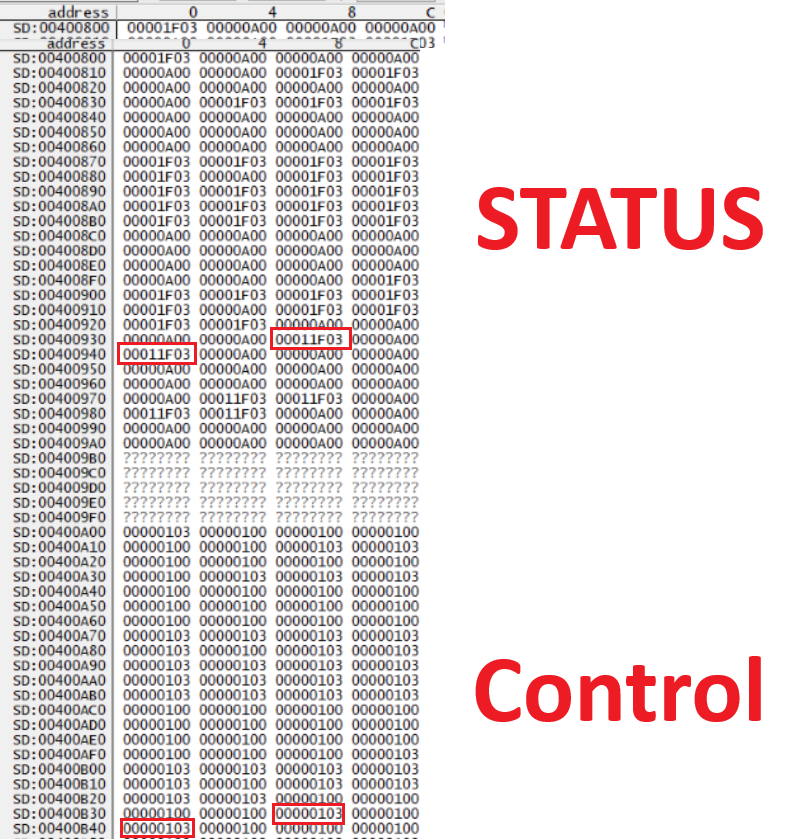

Bellow I present the step by step on we are turning the LPSC OFF, I want to highlight the following A72 LPSC registers:

- LPSC_CLSTER -> 0x400B38

- LPSC_PBIST -> 0x400B3C

- LPSC_0 -> 0x400B40

- LPSC_1 -> 0x400B44

- Ensuring that LPSCs are turned OFF before setting power ON:

- Setting power ON:

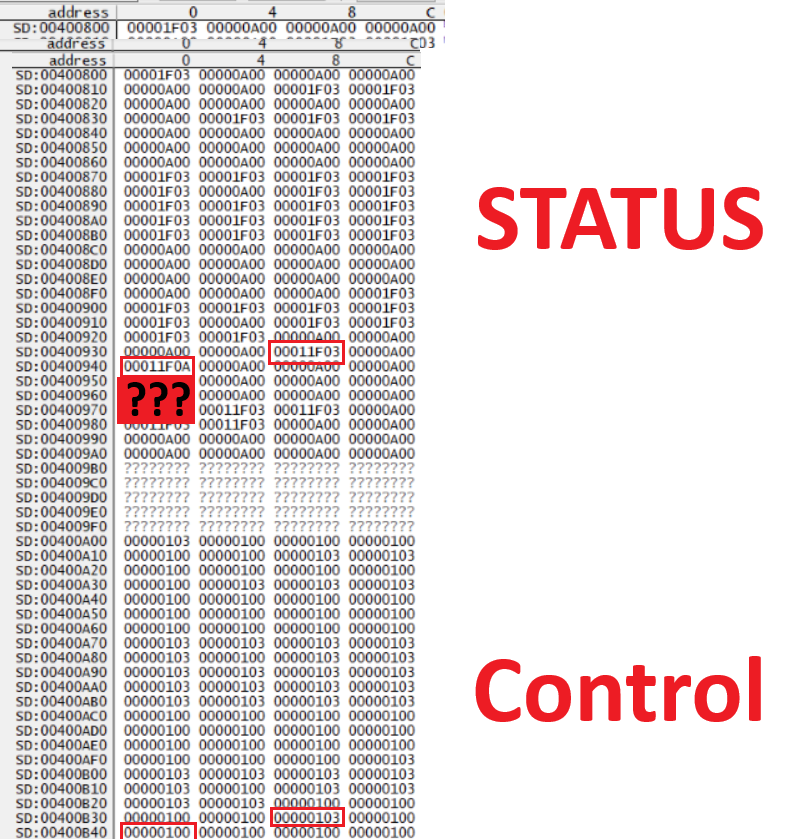

- Then, when we try to power OFF the LPSC of A72 core 0 (0x400B40), it is possible to see that in the Module Status Register of the corresponding LPSC (0x400940), its value is now 0x00011F0A.

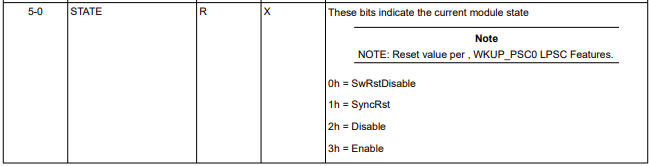

The status bit field, according to the TRM are the bits [5-0], which now represent the status of “001010”.

What is this status?

This status is not described in the TRM.

What must be done to set status to SwRstDisable?

However, as a workaround using the Force bit (bit #31) of the Module Control Register 0x400B40, it is possible to “force” the LPSC to turn OFF.

What is this force bit and how does it really work?

Can we avoid this bit usage?