Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

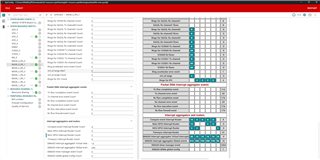

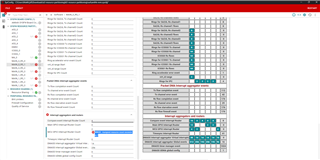

I'm looking to extend a firmware application that's been in development a little while with an GPIO-interrupt counter mechanism. Note that this firmware is running on the R5F0_0 core while Linux is active on the A53 cores. To have an initial test of the HAL API related to GPIO-interrupts I tried the "gpio_interrupt_am64x-evm_r5fss0-0_nortos_ti-arm-clang"-example by loading it in CCS and deploying it through the XDS110 on-board debug probe. The example firmware loads correctly (i.e. enters main) but halts in an assert failure that fires in the "void Module_clockSetFrequency(void)"-function in "ti_power_clock_config.c". See call stack below:

_DebugP_assertNoLog() at DebugP_log.c:119 0x700A286C

Module_clockSetFrequency() at ti_power_clock_config.c:99 0x7008FC40

PowerClock_init() at ti_power_clock_config.c:107 0x70092D0A

System_init() at ti_drivers_config.c:235 0x7009170C

main() at main.c:42 0x700922AE

bypass_auto_init + 0x4 () at boot_armv7r_asm.S:257 0x700A2828

This assert is the result of the "SOC_moduleSetClockFrequency(...)"-call returning -1. The value of "i" in the iteration that failed is 0.

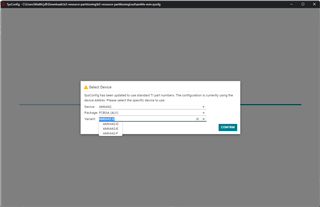

The sysconfig file that came with the example has been unchanged, except the pin the interrupt is set to. This has been changed to the "MCU_SPI1_CLK/D7"-pin. As this is the pin I intend to use in the main project.

To prevent conflict in access to this pin from Linux, the device tree that is active in the kernel has:

&mcu_gpio0 { status = "reserved"; };

&mcu_gpio_intr { status = "reserved";};

added to it. As per documentation https://software-dl.ti.com/mcu-plus-sdk/esd/AM64X/latest/exports/docs/api_guide_am64x/EXAMPLES_DRIVERS_GPIO_INPUT_INTERRUPT.html

The example is built with version 9.1.0.41 of the MCU+SDK if that helps.

I am unsure how the example is still breaking. Any advice on how to resolve this and get GPIO-interrupts working would be appreciated.

Kind regards,

Matthijs