Other Parts Discussed in Thread: TDA4VH

Tool/software:

Hi Master:

My TDA4VH SCH is designed as follow:

1. origin design

lane 0 lane 1 lane 2 land 3

SERDES0 IP2 --> PCIE 4X

SERDES1 IP1 --> Q/SGMII Q/SGMII XFI Disable XFI Disable

SERDES2 IP2 --> None None XFI XFI

SERDES4 IP2 --> Q/SGMII Q/SGMII Q/SGMII Q/SGMII

2. Can be set independently SERDES2 IP1 + IP2 ?

lane 0 lane 1 lane 2 land 3

SERDES0 IP2 --> PCIE 4X

SERDES1 IP1 --> Q/SGMII Q/SGMII Q/SGMII Q/SGMII

*SERDES2 IP1+2--> Q/SGMII Q/SGMII XFI XFI

SERDES4 IP1 --> eDp eDp eDp eDp

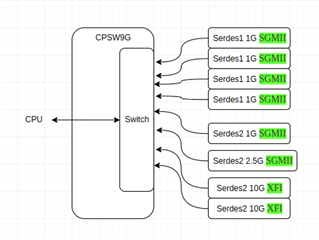

we need 2x10G + 1x2.5G + 5x1G;

It's No2 Can work in BSP?

thanks

Dong Zhang