Tool/software:

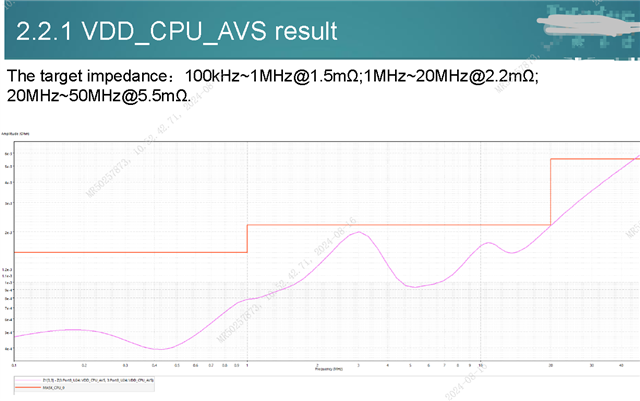

Customer got below PI simulation result:

#1. Margin on 3MHz seems not enough compare to TI provided reference.

#2. >50MHz exceeds TI provided reference, and can't be reduced with current design.

I saw a similar post, my customer's result looks much better than this one:

Is my customer's PI Okay?

Regarding comments in upper post, I understand the first one is recommend to design with more current margin.

But how to do about #2 in design stage, it is more like test procedure.

Max use case performance should be evaluated over SoC silicon fabrication process variations using split lot samples, voltage tolerances and full operational temperature range