Tool/software:

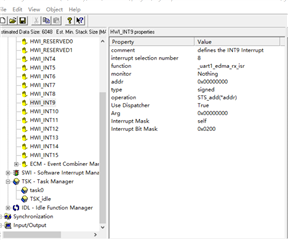

I need add UART driver code into a very old project which developed with DSP/BIOS v5.42.1.9.At first i used EDMA3 to transfer received data from Rx FIFO of UART1 to data buffer in SRAM,two problem appears,one was that EDMATC0 reported "Read address error" because source address was not right,but i was very sure that i wrote the right source address in Parameter Set RAM. Another problem is that the transfer completion interruption can not be serviced even though i already configed ISR for it in tcf file like showing in picture 1 .

but actually the IE9 is not enabled in core register IER .

BTW,the reason leaded to that EDMATC0 reported "Read address error" ,I guessed,is that the onchip 256k SRAM is working as L2 cache.I just uncheck the L2 Cache box in memory brower showing in picture 2,then EDMA works well.But i can't find a place where i can config the way onchip 256k SRAM working in gconf.exe.

As have no idea to solve the two problem,I give up trying to use EDMA,and just use a UART receiver ISR for storing coming data.As the same problem encountered above,the UART receiver interruption can not be serviced.

I want to know how to config the onchip 256k SRAM to work in SRAM not L2 Cache,also why the corresponding bit in IER is not set after configured in gconf.exe