Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi TI support team.

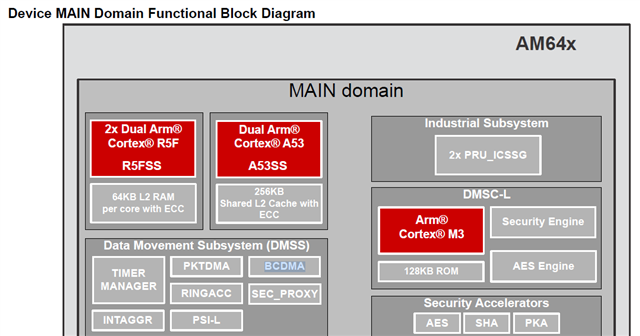

TMDS64EVM's DMA has BCDMA and PKTDMA.

How many channels can be used for each?

Best regards,

Kiyomasa Imaizumi.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Kiyomasa Imaizumi,

Users can go with DMA either BCDMA or PKTDMA channel.

In MCU+SDK, all peripherals uses PKTDMA channels and memory transfer applications uses BCDMA channels .

So, please look at the TRM for more details about channels information.

Here, BCDMA and PKTDMA Tx and Rx Channels enable registers are there.

Based on this account, we can say that the device has these many channels.

Regards,

Anil.

Hello Swargam Anil

Thank you for your reply.

I have some questions.

Q1.

I looked at the TRM.

There is only one BCDMA0, but does that mean that multiple DMA channels are realized by reusing one module called BCDMA0?

Does this mean that if I prepare the DMA settings in memory, I can create unlimited DMA channels?

I don't yet understand the details of BCDMA.

Q2.

I am working on the following BCDMA sample.

udma_memcpy_interrupt_am64x-evm_a53ss0-0_nortos_gcc-aarch64

There are 40 DMA interrupts, from DMASS0_INTAGGR_0_INTAGGR_VINTR_PEND_0 to DMASS0_INTAGGR_0_INTAGGR_VINTR_PEND_39.

When debugging the sample, the interrupt number is 69 (DMASS0_INTAGGR_0_INTAGGR_VINTR_PEND_5).

How is the interrupt number determined?

Q3.

This sample uses one BCDMA.

However, I would like to use two BCDMAs for data communication from DDR to DDR, but I cannot set this in sysconfig.

I would like to know how to implement this, and if there are any samples, please let me know.

Best regards,

Kiyomasa Imaizumi.

There is only one BCDMA0, but does that mean that multiple DMA channels are realized by reusing one module called BCDMA0?

Does this mean that if I prepare the DMA settings in memory, I can create unlimited DMA channels?

I don't yet understand the details of BCDMA.

Yes, your understanding is correct.

With one BCDMA, you can create many DMA channel allocations.

Please look at the syscfg where you can enable multiple DMA channels.

I am working on the following BCDMA sample.

udma_memcpy_interrupt_am64x-evm_a53ss0-0_nortos_gcc-aarch64

There are 40 DMA interrupts, from DMASS0_INTAGGR_0_INTAGGR_VINTR_PEND_0 to DMASS0_INTAGGR_0_INTAGGR_VINTR_PEND_39.

When debugging the sample, the interrupt number is 69 (DMASS0_INTAGGR_0_INTAGGR_VINTR_PEND_5).

How is the interrupt number determined?

Please look at the image below which explains what API does which functionality.

Udma_even register API enables an interrupt for the UDMA completion event for the channel .

Please debug more information in the API .

Mostly, this interrupt is enabled based on the DMA channel numbers .

This sample uses one BCDMA.

However, I would like to use two BCDMAs for data communication from DDR to DDR, but I cannot set this in sysconfig.

I would like to know how to implement this, and if there are any samples, please let me know.

Please look at my 1st comment.

If you need more channels, simply add more channels to syscfg and generate the code .

Next, call TRPD settings for each channel.

Regards,

Anil.