Other Parts Discussed in Thread: AM62A7

Tool/software:

Hi Team,

We are working on DR821 CPU with Linux 09.02 SDK,

We are using IS25WP016D-JNLE spi flash device interfaced with OSPI controller in our custom board, the following issues we are facing while testing this

1. In uboot only single and dual I/O is working properly but Quad mode is not working

spi-tx-bus-width = <4>;

spi-rx-bus-width = <4>;

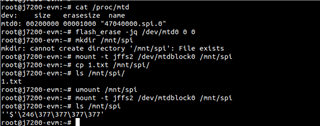

2. In kernel one time data read/write is working proper, but once unmounted and mounted file copied to spi device is getting corrupted but the contents of file is proper, find the attachment of the testcase

This flash device already validated in other custom platforms

Regards,

Nikhil K