Tool/software:

In one of our projects, we are using AM620-Q1_FCBGA441 where there is a necessity of DDR4 interface.

We need help from Texas side for the following details for signal integrity simulation:

1. on-die package decoupling parameters (C and R values).

2. recommended I/O drive strength for DQ,DQS,CLK and ADDRS nets for write and read cycles.

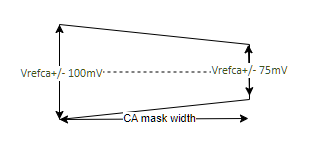

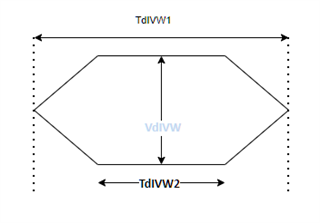

3. Targeted DDR4 eye mask definitions/requirements (CLK,ADDRS, DQ(read & write cycle), DQS(read & write cycle)).