Tool/software:

Hello!

I cannot find absmax drive current for the SPI1_SCLK pin.

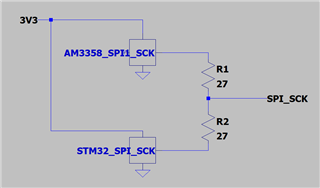

Our design has 2 processors sharing the same copper for the SPI bus. One drives the SPI bus while the other processor is booting.

I would like to know if the AM3358 pin circuit will be damaged if there is a spurious collision, whereby the line is driven low, but the AM3358 is trying to drive it high.

This should not happen per the design, but things happen....

Thanks!

Geof