Tool/software:

Dear TI support,

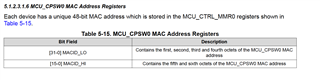

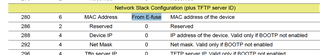

I believe Jacinto processors uses also OTP (eFuse) storage for MAC addresses, is it correct? If yes, then I’d need a tool and instruction (manual) for programming / burning eFuse, would be possible to have it from you? I don’t plan to store a keys in OTP, so I don’t need a keywriter (security functions won’t be used), I just need to add MAC addresses to OTP.

Are following processor variants “High security” versions or “General purpose” versions?

TDA4VM88TGBALFR

DRA829JMTGBALFR

If I update only MAC addresses then is it still possible to burn keys later? I’m not sure if I can program just part of OTP space (program OTP in multiple steps) or only whole OTP space can be programmed (program whole OTP in one step).

Thanks!

Best regards

Libor