Other Parts Discussed in Thread: AM67, SYSCONFIG

Tool/software:

Hi TI experts,

We are adapting the new ddr chip(SAMSUNG 4G K4FBE3D4HB-KHCLT2V) on the EVM board,but uboot spl doesn't seem to start properly.

Here are some action we made:

1.Refer to the new DDR parameters and use the DDR generation tool(SysConfig (ti.com)) to generate a new DDR configuration file.

2.Rename the generated file as k3-j722s-ddr-lp4-50-3733.dtsi and replace the original k3-j722s-ddr-lp4-50-3733.dtsi;

3.modify the memory node in k3-j722s-evm.dts as bellow

question:

1.The new DDR parameters are as bellow file,please help me to check the parameters are correct or not?

TDA4VEntry DDR Config Tool配置参数.xlsx

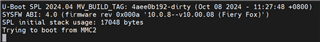

2.Why uboot spl boot failed as bellow picture?

upload the generated files(please rename it as settings_info.syscfg when using):

// @cliArgs --device "J722S_TDA4VEN_TDA4AEN_AM67" --package "AMW" --part "Default" --product "TDA4x_DRA8x_AM67x-AM69x_DDR_Config@0.11.00.0000"

const DDRSS = scripting.addModule("/DDRSS");

DDRSS.system_cfg_soc_number = "AM67x";

DDRSS.system_cfg_ddrss_active = "DDRSS0 Only";

DDRSS.system_cfg_dram_type = "LPDDR4";

DDRSS.system_cfg_msmc_intlv_hybrid = "NA";

DDRSS.system_cfg_msmc_intlv_size = 0;

DDRSS.system_cfg_msmc_intlv_gran = "128 B";

DDRSS.config_fsp0_MHz = 50;

DDRSS.config_fsp1_MHz = 2133;

DDRSS.config_fsp2_MHz = 2133;

DDRSS.lpddr4.config_dram_mr1_rd_pre_FS2 = "Static";

DDRSS.lpddr4.config_dram_mr1_rd_pst_FS2 = "1.5 x tCK";

DDRSS.lpddr4.config_dram_mr3_wr_pst_FS2 = "1.5 x tCK";

DDRSS.lpddr4.config_dram_mr3_dbi_rd_FS2 = "Disable";

DDRSS.lpddr4.config_dram_mr3_dbi_wr_FS2 = "Enable";

DDRSS.lpddr4.config_dram_mr2_rl_FS2 = 32;

DDRSS.lpddr4.config_dram_mr2_wls_FS2 = "WL set A";

DDRSS.lpddr4.config_dram_mr2_wl_FS2 = 16;

DDRSS.lpddr4.config_dram_mr1_nWR_FS2 = 34;

DDRSS.lpddr4.config_dram_odtlon_FS2 = 6;

DDRSS.lpddr4.config_dram_odtloff_FS2 = 26;

DDRSS.lpddr4.config_io_cell_enslicep_drv_dl0_dq = "48 Ohm";

DDRSS.lpddr4.config_io_cell_enslicep_drv_ac = "34.3 Ohm";

DDRSS.lpddr4.config_io_cell_enslicep_drv_cs = "34.3 Ohm";

DDRSS.lpddr4.config_io_cell_enslicep_odt_dl0_dq = "Hi-Z";

DDRSS.lpddr4.config_io_cell_enslicen_odt_dl0_dq = "48 Ohm";

DDRSS.lpddr4.config_dram_mr14_vr_dq_FS2 = "Range 0";

DDRSS.lpddr4.config_dram_mr14_vref_dq_FS2 = 16;

DDRSS.lpddr4.config_dram_mr12_vr_ca_FS2 = "Range 0";

DDRSS.lpddr4.config_dram_mr12_vref_ca_FS2 = 25.6;

DDRSS.lpddr4.config_dram_mr3_pdds_FS2 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_mr3_pu_cal_FS2 = "VDDQ / 3";

DDRSS.lpddr4.config_dram_mr22_odtd_ca_FS2 = "ODT_CA Bond Pad";

DDRSS.lpddr4.config_dram_mr22_odte_ck_FS2 = "Enable";

DDRSS.lpddr4.config_dram_mr22_odte_cs_FS2 = "Enable";

DDRSS.lpddr4.config_dram_mr11_ca_odt_FS2 = "RZQ/4(60ohm)";

DDRSS.lpddr4.config_dram_mr11_dq_odt_FS2 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_mr22_soc_odt_FS2 = "RZQ/5(48ohm)";

DDRSS.lpddr4.system_cfg_dram_width = 32;

DDRSS.lpddr4.system_cfg_dram_density = 16;

DDRSS.lpddr4.system_cfg_dram_ranks = 2;

DDRSS.lpddr4.system_cfg_temp_range = "> 85C";

DDRSS.lpddr4.system_cfg_dram_mr4_poll = "No";

DDRSS.lpddr4.system_cfg_sys_temp_grad = 30;

DDRSS.lpddr4.system_cfg_lpm = "No";

DDRSS.lpddr4.system_cfg_fastboot = "No";

DDRSS.lpddr4.system_cfg_periodic_train = "Yes";

DDRSS.lpddr4.config_dram_mr1_bl_FS0 = "16 sequential";

DDRSS.lpddr4.config_dram_mr1_bl_FS1 = "16 sequential";

DDRSS.lpddr4.config_dram_mr1_bl_FS2 = "16 sequential";

DDRSS.lpddr4.config_dram_mr1_rd_pre_FS0 = "Static";

DDRSS.lpddr4.config_dram_mr1_rd_pre_FS1 = "Static";

DDRSS.lpddr4.config_dram_mr1_rd_pst_FS0 = "1.5 x tCK";

DDRSS.lpddr4.config_dram_mr1_rd_pst_FS1 = "1.5 x tCK";

DDRSS.lpddr4.config_dram_mr3_wr_pst_FS0 = "1.5 x tCK";

DDRSS.lpddr4.config_dram_mr3_wr_pst_FS1 = "1.5 x tCK";

DDRSS.lpddr4.config_dram_mr3_dbi_rd_FS0 = "Disable";

DDRSS.lpddr4.config_dram_mr3_dbi_rd_FS1 = "Disable";

DDRSS.lpddr4.config_dram_mr3_dbi_wr_FS0 = "Enable";

DDRSS.lpddr4.config_dram_mr3_dbi_wr_FS1 = "Enable";

DDRSS.lpddr4.config_dram_mr2_rl_FS0 = 6;

DDRSS.lpddr4.config_dram_mr2_wls_FS0 = "WL set A";

DDRSS.lpddr4.config_dram_mr2_wl_FS0 = 4;

DDRSS.lpddr4.config_dram_mr1_nWR_FS0 = 6;

DDRSS.lpddr4.config_dram_odtlon_FS0 = 0;

DDRSS.lpddr4.config_dram_odtloff_FS0 = 0;

DDRSS.lpddr4.config_dram_mr2_rl_FS1 = 32;

DDRSS.lpddr4.config_dram_mr2_wls_FS1 = "WL set A";

DDRSS.lpddr4.config_dram_mr2_wl_FS1 = 16;

DDRSS.lpddr4.config_dram_mr1_nWR_FS1 = 34;

DDRSS.lpddr4.config_dram_odtlon_FS1 = 6;

DDRSS.lpddr4.config_dram_odtloff_FS1 = 26;

DDRSS.lpddr4.config_dram_tINIT1_ns = 200000;

DDRSS.lpddr4.config_dram_tINIT2_ns = 10;

DDRSS.lpddr4.config_dram_tINIT3_ns = 2000000;

DDRSS.lpddr4.config_dram_tINIT4_tCK = 5;

DDRSS.lpddr4.config_dram_tINIT5_ns = 2000;

DDRSS.lpddr4.UNREFERENCED = 100;

DDRSS.lpddr4.config_dram_tREFIab_ns = 3904;

DDRSS.lpddr4.config_dram_tREFIpb_ns = 488;

DDRSS.lpddr4.config_dram_tRFCab_ns = 280;

DDRSS.lpddr4.config_dram_tRFCpb_ns = 140;

DDRSS.lpddr4.config_dram_tVRCG_ENABLE_ns = 200;

DDRSS.lpddr4.config_dram_tVRCG_DISABLE_ns = 100;

DDRSS.lpddr4.config_dram_tOSCO_tCK = 8;

DDRSS.lpddr4.config_dram_tOSCO_ns = 40;

DDRSS.lpddr4.config_dram_tZQCAL_ns = 1000;

DDRSS.lpddr4.config_dram_tZQLAT_tCK = 8;

DDRSS.lpddr4.config_dram_tZQLAT_ns = 30;

DDRSS.lpddr4.config_dram_tZQRESET_tCK = 3;

DDRSS.lpddr4.config_dram_tZQRESET_ns = 50;

DDRSS.lpddr4.config_dram_tFClong_ns = 250;

DDRSS.lpddr4.config_dram_tCKFSPE_tCK = 4;

DDRSS.lpddr4.config_dram_tCKFSPE_ns = 7.5;

DDRSS.lpddr4.config_dram_tCKFSPX_tCK = 4;

DDRSS.lpddr4.config_dram_tCKFSPX_ns = 7.5;

DDRSS.lpddr4.config_dram_tDQSCKmin_ns = 1.5;

DDRSS.lpddr4.config_dram_tDQSCKmax_ns = 3.5;

DDRSS.lpddr4.config_dram_tCKE_tCK = 4;

DDRSS.lpddr4.config_dram_tCKE_ns = 7.5;

DDRSS.lpddr4.config_dram_tCMDCKE_tCK = 3;

DDRSS.lpddr4.config_dram_tCMDCKE_ns = 1.75;

DDRSS.lpddr4.config_dram_tCKELCK_tCK = 5;

DDRSS.lpddr4.config_dram_tCKELCK_ns = 5;

DDRSS.lpddr4.config_dram_tCSCKE_ns = 1.75;

DDRSS.lpddr4.config_dram_tCKELCS_tCK = 5;

DDRSS.lpddr4.config_dram_tCKELCS_ns = 5;

DDRSS.lpddr4.config_dram_tCKCKEH_tCK = 3;

DDRSS.lpddr4.config_dram_tCKCKEH_ns = 1.75;

DDRSS.lpddr4.config_dram_tXP_tCK = 5;

DDRSS.lpddr4.config_dram_tXP_ns = 7.5;

DDRSS.lpddr4.config_dram_tCSCKEH_ns = 1.75;

DDRSS.lpddr4.config_dram_tCKEHCS_tCK = 5;

DDRSS.lpddr4.config_dram_tCKEHCS_ns = 7.5;

DDRSS.lpddr4.config_dram_tMRWCKEL_tCK = 10;

DDRSS.lpddr4.config_dram_tMRWCKEL_ns = 14;

DDRSS.lpddr4.config_dram_tZQCKE_tCK = 3;

DDRSS.lpddr4.config_dram_tZQCKE_ns = 1.75;

DDRSS.lpddr4.config_dram_tMRW_tCK = 10;

DDRSS.lpddr4.config_dram_tMRW_ns = 10;

DDRSS.lpddr4.config_dram_tMRD_tCK = 10;

DDRSS.lpddr4.config_dram_tMRD_ns = 14;

DDRSS.lpddr4.config_dram_tMRR_tCK = 8;

DDRSS.lpddr4.config_dram_tMRRI_tCK = 20;

DDRSS.lpddr4.config_dram_tSDO_tCK = 12;

DDRSS.lpddr4.config_dram_tSDO_ns = 20;

DDRSS.lpddr4.config_dram_tSR_tCK = 3;

DDRSS.lpddr4.config_dram_tSR_ns = 15;

DDRSS.lpddr4.config_dram_tXSR_tCK = 2;

DDRSS.lpddr4.config_dram_tXSR_ns = 287.5;

DDRSS.lpddr4.config_dram_tCCD_tCK = 8;

DDRSS.lpddr4.config_dram_tCCDMW_tCK = 32;

DDRSS.lpddr4.config_dram_tRTP_tCK = 8;

DDRSS.lpddr4.config_dram_tRTP_ns = 7.5;

DDRSS.lpddr4.config_dram_tRCD_tCK = 4;

DDRSS.lpddr4.config_dram_tRCD_ns = 18;

DDRSS.lpddr4.config_dram_tRPpb_tCK = 4;

DDRSS.lpddr4.config_dram_tRPpb_ns = 18;

DDRSS.lpddr4.config_dram_tRPab_tCK = 4;

DDRSS.lpddr4.config_dram_tRPab_ns = 21;

DDRSS.lpddr4.config_dram_tRASmin_tCK = 3;

DDRSS.lpddr4.config_dram_tRASmin_ns = 42;

DDRSS.lpddr4.config_dram_tRASmax_ns = 35136;

DDRSS.lpddr4.config_dram_tWR_tCK = 6;

DDRSS.lpddr4.config_dram_tWR_ns = 18;

DDRSS.lpddr4.config_dram_tWTR_tCK = 8;

DDRSS.lpddr4.config_dram_tWTR_ns = 10;

DDRSS.lpddr4.config_dram_tRRD_tCK = 4;

DDRSS.lpddr4.config_dram_tRRD_ns = 10;

DDRSS.lpddr4.config_dram_tPPD_tCK = 4;

DDRSS.lpddr4.config_dram_tFAW_tCK = 0;

DDRSS.lpddr4.config_dram_tFAW_ns = 40;

DDRSS.lpddr4.config_dram_tESCKE_tCK = 3;

DDRSS.lpddr4.config_dram_tESCKE_ns = 1.75;

DDRSS.lpddr4.config_dram_tDStrain_ns = 2;

DDRSS.lpddr4.config_dram_tADR_ns = 20;

DDRSS.lpddr4.config_dram_tCAENT_ns = 250;

DDRSS.lpddr4.config_dram_tVREFcalong_ns = 250;

DDRSS.lpddr4.config_dram_tVREFcashort_ns = 80;

DDRSS.lpddr4.config_dram_tCKEHDQS_ns = 10;

DDRSS.lpddr4.config_dram_tMRZ_ns = 1.5;

DDRSS.lpddr4.config_dram_tODTonMIN_ns = 1.5;

DDRSS.lpddr4.config_dram_tODTonMAX_ns = 3.5;

DDRSS.lpddr4.config_dram_tODToffMIN_ns = 1.5;

DDRSS.lpddr4.config_dram_tODToffMAX_ns = 3.5;

DDRSS.lpddr4.config_dram_tTSI_ns = 32000000;

DDRSS.lpddr4.config_dram_TempMargin_ns = 2;

DDRSS.lpddr4.config_io_cell_mode_dl0 = "Range 0";

DDRSS.lpddr4.config_io_cell_vrefsel_dl0 = 16.7;

DDRSS.lpddr4.config_io_cell_mode_ac = "Range 0";

DDRSS.lpddr4.config_io_cell_vrefsel_ac = 16.7;

DDRSS.lpddr4.config_io_cell_enslicep_drv_dl0_dqs = "48 Ohm";

DDRSS.lpddr4.config_io_cell_enslicen_drv_dl0_dq = "48 Ohm";

DDRSS.lpddr4.config_io_cell_enslicen_drv_dl0_dqs = "48 Ohm";

DDRSS.lpddr4.config_io_cell_enslicen_drv_ac = "34.3 Ohm";

DDRSS.lpddr4.config_io_cell_enslicen_drv_cs = "34.3 Ohm";

DDRSS.lpddr4.config_io_cell_enslicep_odt_dl0_dqs = "Hi-Z";

DDRSS.lpddr4.config_io_cell_enslicen_odt_dl0_dqs = "48 Ohm";

DDRSS.lpddr4.config_dram_mr14_vr_dq_FS0 = "Range 0";

DDRSS.lpddr4.config_dram_mr14_vr_dq_FS1 = "Range 0";

DDRSS.lpddr4.config_dram_mr14_vref_dq_FS0 = 16;

DDRSS.lpddr4.config_dram_mr14_vref_dq_FS1 = 16;

DDRSS.lpddr4.config_dram_mr12_vr_ca_FS0 = "Range 0";

DDRSS.lpddr4.config_dram_mr12_vr_ca_FS1 = "Range 0";

DDRSS.lpddr4.config_dram_mr12_vref_ca_FS0 = 25.6;

DDRSS.lpddr4.config_dram_mr12_vref_ca_FS1 = 25.6;

DDRSS.lpddr4.config_dram_mr3_pdds_FS0 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_mr3_pdds_FS1 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_mr3_pu_cal_FS0 = "VDDQ / 3";

DDRSS.lpddr4.config_dram_mr3_pu_cal_FS1 = "VDDQ / 3";

DDRSS.lpddr4.config_dram_mr22_odtd_ca_FS0 = "ODT_CA Bond Pad";

DDRSS.lpddr4.config_dram_mr22_odtd_ca_FS1 = "ODT_CA Bond Pad";

DDRSS.lpddr4.config_dram_mr22_odte_ck_FS0 = "Enable";

DDRSS.lpddr4.config_dram_mr22_odte_ck_FS1 = "Enable";

DDRSS.lpddr4.config_dram_mr22_odte_cs_FS0 = "Enable";

DDRSS.lpddr4.config_dram_mr22_odte_cs_FS1 = "Enable";

DDRSS.lpddr4.config_dram_mr11_ca_odt_FS0 = "RZQ/4(60ohm)";

DDRSS.lpddr4.config_dram_mr11_ca_odt_FS1 = "RZQ/4(60ohm)";

DDRSS.lpddr4.config_dram_mr11_dq_odt_FS0 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_mr11_dq_odt_FS1 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_mr22_soc_odt_FS0 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_mr22_soc_odt_FS1 = "RZQ/5(48ohm)";

DDRSS.lpddr4.config_dram_byteswap_01 = "No";

DDRSS.lpddr4.config_dram_byteswap_23 = "No";

DDRSS.lpddr4.config_dram_DQ0 = "Memory DQ0";

DDRSS.lpddr4.config_dram_DQ1 = "Memory DQ1";

DDRSS.lpddr4.config_dram_DQ2 = "Memory DQ2";

DDRSS.lpddr4.config_dram_DQ3 = "Memory DQ3";

DDRSS.lpddr4.config_dram_DQ4 = "Memory DQ4";

DDRSS.lpddr4.config_dram_DQ5 = "Memory DQ5";

DDRSS.lpddr4.config_dram_DQ6 = "Memory DQ6";

DDRSS.lpddr4.config_dram_DQ7 = "Memory DQ7";

DDRSS.lpddr4.config_dram_DQ8 = "Memory DQ8";

DDRSS.lpddr4.config_dram_DQ9 = "Memory DQ9";

DDRSS.lpddr4.config_dram_DQ10 = "Memory DQ10";

DDRSS.lpddr4.config_dram_DQ11 = "Memory DQ11";

DDRSS.lpddr4.config_dram_DQ12 = "Memory DQ12";

DDRSS.lpddr4.config_dram_DQ13 = "Memory DQ13";

DDRSS.lpddr4.config_dram_DQ14 = "Memory DQ14";

DDRSS.lpddr4.config_dram_DQ15 = "Memory DQ15";

DDRSS.lpddr4.config_dram_DQ16 = "Memory DQ16";

DDRSS.lpddr4.config_dram_DQ17 = "Memory DQ17";

DDRSS.lpddr4.config_dram_DQ18 = "Memory DQ18";

DDRSS.lpddr4.config_dram_DQ19 = "Memory DQ19";

DDRSS.lpddr4.config_dram_DQ20 = "Memory DQ20";

DDRSS.lpddr4.config_dram_DQ21 = "Memory DQ21";

DDRSS.lpddr4.config_dram_DQ22 = "Memory DQ22";

DDRSS.lpddr4.config_dram_DQ23 = "Memory DQ23";

DDRSS.lpddr4.config_dram_DQ24 = "Memory DQ24";

DDRSS.lpddr4.config_dram_DQ25 = "Memory DQ25";

DDRSS.lpddr4.config_dram_DQ26 = "Memory DQ26";

DDRSS.lpddr4.config_dram_DQ27 = "Memory DQ27";

DDRSS.lpddr4.config_dram_DQ28 = "Memory DQ28";

DDRSS.lpddr4.config_dram_DQ29 = "Memory DQ29";

DDRSS.lpddr4.config_dram_DQ30 = "Memory DQ30";

DDRSS.lpddr4.config_dram_DQ31 = "Memory DQ31";

Regards.