Tool/software:

Hi C6748 Champ !

My customer uses TMS320C6748EZCEA3 part for their next model.

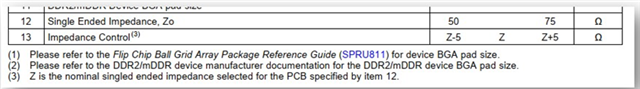

HW engineer would like to check impedance related. He found the following descriptions.

His understanding was that the impedance (Z0) could be 50 to 75 ohm design and 45 to 55 ohm with +/- 5 ohm for a 50 ohm design.

Then, when designing the PCB, please confirm whether it is possible to calculate 50 ohm for the layer mounting the IC and 47 ohm for the Data Line Layer and design the PCB.

I would like a quick and accurate confirmation as I will pass it to the PCB manufacturer.

Thanks

Best Regards,

Jack