Tool/software:

Hello,

I have a question regarding the distribution of the GPIO interrupts, once in firmware mcu1_0 and once on the mpu1 (A72 Linux).

Board: J784s4 custom board

PDK: 09.02.00.30

Linux

SPL Boot

In our current setup, we have added the two gpio banks ‘wkup_gpio0’ and ‘main_gpio0’ to the Linux by the assistance of the device tree.

because some of the WKUP Pins are used by

&main_gpio0 {

status = "okay";

pinctrl-names = "default";

gpio-line-names = MAIN_GPIO0_LINE_NAMES;

};

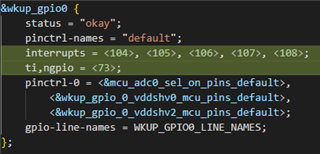

&wkup_gpio0 {

status = "okay";

pinctrl-names = "default";

gpio-line-names = WKUP_GPIO0_LINE_NAMES;

};

We have also configured the GPIO driver in the mcu1-0 firmware so that it reacts to a rising edge on the pin and is currently working as expected.

The pin, which is used in the Mcu1_0, to trigger a Interrupt handler is the WKUP_GPIO0_0 -> H38.

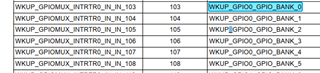

According to the reference manual, I have seen that 16 GPIO pins always share one ISR vector, in our case ISR vector 103

is affected.

Problem:

Now I have problem that the "gpio-davinic.c" linux driver is complaining about a error that an IRQ 103

can not be requested, and the probe fails because the Interrupt resource is already in usage (Interrupt Vector 103)

elixir.bootlin.com/.../gpio-davinci.c

At the "wkup_gpio0" device tree node, the interrupt vectors

interrupts = <103>, <104>, <105>, <106>, <107>, <108> are assiged to the

device.

wkup_gpio0: gpio@42110000 {

compatible = "ti,j721e-gpio", "ti,keystone-gpio";

reg = <0x00 0x42110000 0x00 0x100>;

gpio-controller;

#gpio-cells = <2>;

interrupt-parent = <&wkup_gpio_intr>;

interrupts = <103>, <104>, <105>, <106>, <107>, <108>;

interrupt-controller;

#interrupt-cells = <2>;

ti,ngpio = <89>;

ti,davinci-gpio-unbanked = <0>;

power-domains = <&k3_pds 167 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 167 0>;

clock-names = "gpio";

status = "disabled";

};

I was able to solve the problem prototypical by deleting the ISR Vector 103 from the node

and reduce the number of available gpios by 16.

My Questions:

1; Is it really good idea to split up interrupt vectors from a gpio controller between tow different domains (main a72 and wakup mcu1-0)?

2; What is the Ti preferred way to avoid such distribution problems, like interrupts?

3; Assuming we have the case that any gpio interrupt in the mcu-1-0 domain that is required and is sharing the same interrupt vector with another pin on the a72 linux.

The prototypical described way with the interrupt distribution would not work?

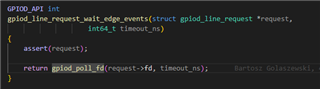

In linux the libgpiod feature to wait for an event is also used.

Kind Regards

Thomas