Tool/software:

Hello,

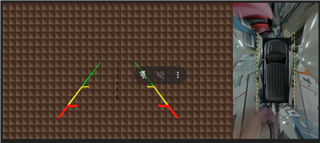

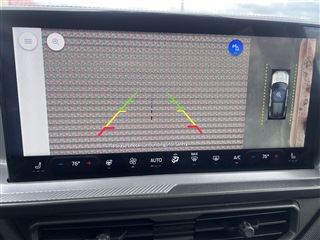

We have another corrupted image coming from a vehicle. Issue was persistent while shift from Drive to Reverse (Please see the video). and it recovered in the same cycle.

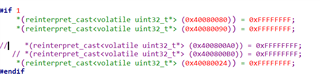

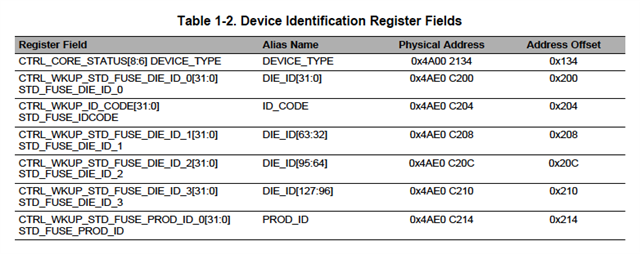

Please urgently support us on how can we get such behavior knowing that our rendering process is map to EVE core. So is there any kind of flag error that we can check on or what can we check on EVE to investigate this issue.

Waiting for feedback.

Thanks