Tool/software:

Hi TI Experts,

Could you guide me on testing Partial IO LPM using the SK for UART or USB

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi TI Experts,

Could you guide me on testing Partial IO LPM using the SK for UART or USB

Hi Board designers,

Refer below recommendations for AM62A SK hardware changes to testing Partial IO LPM

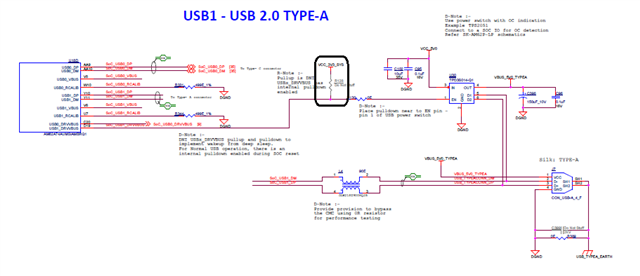

USB

The USBx_DRVVBUS used to enable the USB power switch has an internal pulldown enabled during reset and after reset.

In the SK, an external pullup is provided. This needs to be enabled.

In any of the SK if an external pullup or pulldown is provided, both of these pulls should be made DNI.

UART

The below document describes the changes to be made

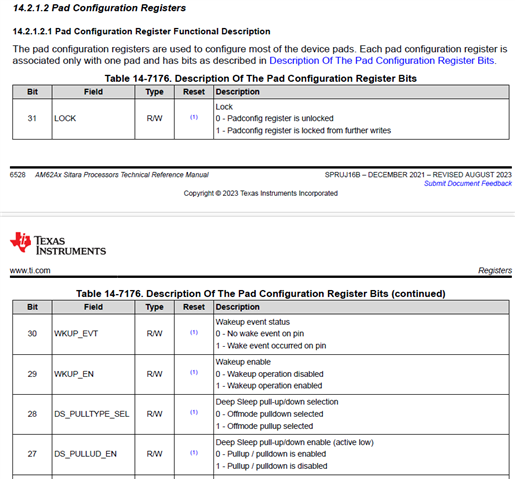

Pad Configuration

Refer Bit-29

Additional references

3.3.5. Low Power Modes — Processor SDK AM62x Documentation

Regards,

Sreenivasa

Hi Board designers,

Generation of VDD_CANUART supply

Deriving VDDSHV_CANUART from VCC_3V3_MAIN

Regards,

Sreenivasa

Hi Board designers,

Refer below for Partial IO mode functionality:

The Partial IO circuits will be disabled the first time power is applied to the processor. When the Partial IO circuits are disable, the MCU_PORz signal will propagate to these circuits. The MCU_PORz signal is blocked from these circuits after software enables the Partial IO functionality (circuits) and configures the processor to monitor wake-up inputs. This is necessary since the MCU_PORz signal will be asserted by the PMIC when it begins the power down sequence associated with the other processor power rails.

Regards,

Sreenivasa