Other Parts Discussed in Thread: DRA821

Tool/software:

Is the EyeSurf in cadence phy disabled?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Is the EyeSurf in cadence phy disabled?

Kimmo,

Do you have the background of this request? What are you trying to do and what do you have currently in terms of sw? Have you written or trying to write your eye surf s/w code or trying to use any built-in code and not seeing the expected output?

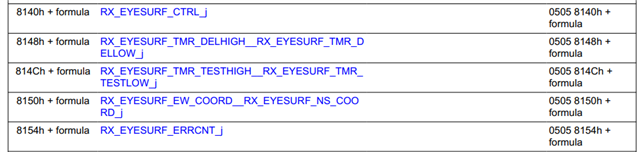

I tried to write some adhoc sw, as i got inspired by this video https://www.youtube.com/watch?v=uCPw_6TN8H0 and noticed some EYESURF named registers on the J721E register documentation

and some bits controlling RX e paths.

I do not have any further information for this. I tried to set the timer registers to non-zero value, but they keep reading back 0.

(Accessing SERDES_10G1 at 0x0005060000)

Thank you for the background and the youtube video. I think I know that person talking!

J721E is a different IP than that we have in the DRA821; so the same registers would not apply directly to this SoC.

This IP has a few register writes to enable the eye tool and for the default run, these registers are disabled to conserve power. The RX error path RX_PSC_A1_RX_PSC_A0[1] and [17] and the diagnostic switched power island controller CMN_CDIAG_PWRI_OVRD_CMN_CDIAG_XCVRC_PWRI_STAT [31], [25] must be enabled after the SERDES POR RST and before the SERDES release reset and run the eye surf code to collect the eye data.

Ok, thanks for the information. I'll continue with this when i have some spare time.