Tool/software:

Hi there!

In the R5F IPC example with spinlock the id 0 is used.

How do I know which one is free? Not already use by default by the Linux drivers in the kernel.

Regards.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi there!

In the R5F IPC example with spinlock the id 0 is used.

How do I know which one is free? Not already use by default by the Linux drivers in the kernel.

Regards.

Hi Nelson,

Thanks for your query.

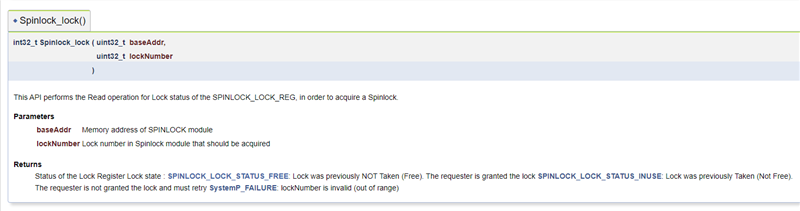

To check whether a spinlock is free to use or not. Use the Spinlock_lock() API.

Please refer below image.

Please refer Spinlock_API for more details.

Regards,

Tushar

Hello there Tushar. Thanks for your reply.

What I'm wondering is what spinlock ID to use, from the 256 available, so that it's not used by a Linux driver. I see this entry in the DTS but from there I dont't know how to tell.

hwspinlock: spinlock@2a000000 { compatible = "ti,am64-hwspinlock"; reg = <0x00 0x2a000000 0x00 0x1000>; #hwlock-cells = <1>; };

The motivations for this question are both performance and stability (the other process might hang leaving it blocked).

Regards.

Hi Nelson,

I know this sounds confusing, but Linux initializes all the 256 hwspinlocks (if the hwspinlock node is not disabled in kernel devicetree), but doesn't use any of them. Linux kernel uses sw spinlocks.

Bin:

(cc: (+) Tushar Thakur's Profile - Tushar Thakur - TI E2E support forums & (+) Nick Saulnier's Profile - Nick Saulnier - TI E2E support forums )

The fact that A53 cores have hardware spinlocks versus the Linux kernel software spinlocks should be distinguished in the upcoming ver 10 AM64x Academies (another input wrt e2e entry (+) AM6442: Can the AM64x ver 10 academy be ready in mid October? - Processors forum - Processors - TI E2E support forums ). You should not confuse the end users which spinlock to use in Sitara applications.

later, Jim

Jim,

Thanks for the feedback.

I will defer this to Tushar or Nick on how to address in the MCU SDK documentation.

Hi there. Since there were clarifications just to be sure: Then I'm OK choosing any HW spinlock (0 - 255) because Linux doesn't use them.

Wondering if the ICSSG Ethernet drivers use any. Other that that we don't intend to run R5F or PRU code that is not ours.

Hi Nelson,

Since Linux doesn't use it, the ICSSG Ethernet kernel driver doesn't use hwspinlock, but I don't if the PRU firmware for ICSSG Ethernet uses hwspinlock or not, I am routing your query to our ICSSG Ethernet expert for comments.

Hello Jim,

We specifically do not discuss spinlocks in the Multicore academy section, so I only briefly mention it here:

https://dev.ti.com/tirex/explore/node?a=7qm9DIS__LATEST&node=A__AfVdz15iX-WmL3U4FSsSXQ__AM64-ACADEMY__WI1KRXP__LATEST

However, I can add a note that software spinlocks also exist, and are not documented in the multicore academy.

We do not document that any hardware spinlocks are used, but I will send the thread to the PRU firmware team to confirm.

Regards,

Nick

Hi Jim,

PRU firmware and Enet LLD (ICSSG Ethernet driver) does not use any Hw spinlocks.

Regards,

Prajith

I have added a little more information about spinlocks to the AM64x multicore academy on our backend. Depending on when I can get a code review & signoff, the academy may be updated this week, or it may not be updated until sometime next week.

https://dev.ti.com/tirex/explore/node?node=A__AfVdz15iX-WmL3U4FSsSXQ__AM64-ACADEMY__WI1KRXP__LATEST

Regards,

Nick