Tool/software:

Background

Errata ID: i2437 refers to the C7x Streaming Engine (SE). This errata applies to J721S2 and J784S4 and the details can be found in their respective Processor

Silicon Revision documents. Note that this is specific for SoCs that use the specific C7x variant, C7120, so Jacinto SoCs such as J721E (C7100) and J722S (C7524) are not affected by this errata, and further steps do not need to be taken.

A screenshot of the errata is included below for reference:

Due to a hardware bug in the streaming engine's high level clock gating logic, the C7120 CPU can hang when executing applications that include usage of the streaming engine to read from memory. This can occur regardless of how the streaming engine parameters (e.g. the element type, dimension of the pattern, etc.) are programmed during initialization of the desired data access pattern. Overriding this higher level clock gating logic can prevent this particular issue where the hang is caused by various Corepac components being mistakenly idle. The issue can present on both SE0 and SE1.

Symptoms

This issue will present itself during usage of Streaming Engine in programs, during OPEN, ADV, and CLOSE operations. Generally, replication of the issue is not consistent, and for example, can happen at varying points in an execution loop with SE during repeated testing. The resultant behavior is a hang of the C7x CPU, in which a system reboot would need to be performed to recover. To better diagnose the issue, having a full register dump of the C7x core after the core hang is beneficial. If debugging with CCS, entering "Force Debug" after the hang occurs, will allow you to get this register snapshot.

Workaround

The given workaround is to enable the DSP_<COREID>_DEBUG_CLKEN_OVERRIDE fields in the COMPUTE_CLUSTER_CFG_WRAP_0_CC_CNTRL register. COREID refers to the specific C7x core to enable the override field for. In the case of J721S2 with 2 C7x cores, there are two such fields (DSP_5_DEBUG_CLKEN_OVERRIDE, DSP_4_DEBUG_CLKEN_OVERRIDE) and for J784S4 with 4 C7x cores, there are four such fields (DSP_7_DEBUG_CLKEN_OVERRIDE, DSP_6_DEBUG_CLKEN_OVERRIDE, DSP_5_DEBUG_CLKEN_OVERRIDE, DSP_4_DEBUG_CLKEN_OVERRIDE). This register is described with the Technical Reference Manual (TRM) register spreadsheets in the "COMPUTE_CLUSTER_CFG_WRA" sheet, and a screenshot below of these register fields in the case of J784S4 is shown:

For reference, the full description of the field is "DSP I0/I1 clock gate override. Can be used to override DSP I0/I1 clock enables for debug on all instances. This bit has to set before AC71 powerup. 1 - Override I0/I1 clock enable on all DSP instances in compute cluster"

Patch

As stated in the description, the workaround must be implemented before the C7x core is powered up. An example of this workaround can be applied in the SBL bootflow with the PDK package as given in the attached patch file. The similar principle can be applied in BootApp, SPL, etc as long as this caveat is met.

The patch configures a Region Address Table (RAT) on the MCU1_0 in order to access a 64-bit register at 0x4D21000200, the write to the required register is done, and the RAT is de-configured for future use.

REGION0 is used for the RAT configuration, and a base address of 0xC0000000 is used. The upper address and lower address split the address of 0x4D21000000. The CTRL register is then set to enable the RAT. The address that is then written to is 0xC0000200 which is the base address of 0xC0000000 + a 0x200 offset to access 0x4D21000200. The value written then differs based on the number of DSP_<COREID>_DEBUG_CLKEN_OVERRIDE fields there are for each SoC:

In the case of J721S2:

0x00000300 → This corresponds to setting DSP_5_DEBUG_CLKEN_OVERRIDE and DSP_4_DEBUG_CLKEN_OVERRIDE to 1. This enables the override for both cores on the SoC.

In the case of J784S4:

0x00000F00 → This corresponds to setting DSP_7_DEBUG_CLKEN_OVERRIDE, DSP_6_DEBUG_CLKEN_OVERRIDE, DSP_5_DEBUG_CLKEN_OVERRIDE, and DSP_4_DEBUG_CLKEN_OVERRIDE to 1. This enables the override for all 4 cores on the SoC.

The RAT CTRL register is then set to disable the RAT. The other RAT configurations are then cleared.

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/0001_2D00_i2437_2D00_Errata_2D00_patch_2D00_for_2D00_disabling_2D00_streaming_2D00_engine_2D00_cl.patch

Testing and Validation

This has been tested with PROCESSOR-SDK-RTOS 10.0. If you are using an older SDK, have made modifications to SBL, or want to implement the workaround in a different part of the bootflow, note that you may need to adjust the RAT configuration based on your memory map or other usage of the RAT region that is used by default in the patch. Further information on RAT configuration can be found in the TRM for your SoC.

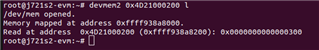

To tell if the patch is applied properly, you can access the patch via the DAP port of your debugger at the register address of 0x4D21000200 or use devmem2 at that same address.

Ex: