Tool/software:

Dear Hardware expert:

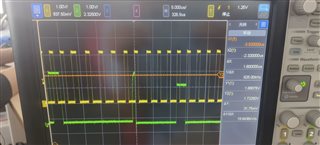

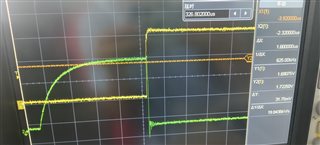

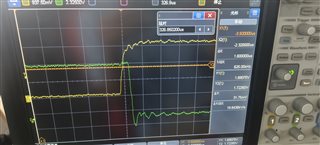

I am testing J784S4's mdio timing. found that its MDIO(AE37 AC36) 's signal is wired.

Note: green line is MDIO The yelow line is MDC

My question:

1、Why MDC‘s +width is not equal -width

2、 Why MDIO's some bit's rise time slow , and its fall line is just as MDC's rise line??

Is there a error here? How can i optimize here?