Other Parts Discussed in Thread: TDA4VM

Tool/software:

At 1866MHz Clock Speed the device fails to boot and gets stuck at the uboot prompt after "I/TC: Primary CPU switching to normal world boot". This board has already successfully booted when clock is set at 1600MHz and 2133MHz. Unsure why at 1866MHz it would fail.

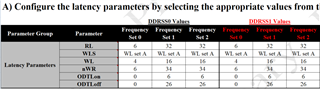

Only parameters changed between the 1600MHz and the 1866 MHz were the Latency parameters shown below and obviously the Memory frequency. Already made sure they match the DRAM devices datasheet.

After running the tda4vm_lp4_debug.out it shows a dfi_rddata_valid timeout and PLL Frequency Error. Is 1866MHz a supported frequency?

[MCU_Cortex_R5_0] DDRSS0 Training Results: Training Results; Frequency 0; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x20 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x1f DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x20 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 348 CA Bit 1 delay: 338 CA Bit 2 delay: 34c CA Bit 3 delay: 33e CA Bit 4 delay: 34e CA Bit 5 delay: 34e Write Leveling: DQ Lane 0 WRDQS: 0xa8 DQ Lane 1 WRDQS: 0xc6 DQ Lane 2 WRDQS: 0x72 DQ Lane 3 WRDQS: 0xa8 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 16 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 480 lat_adj: 4 DQS Gate Lane 2 : slave_delay: 52 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 492 lat_adj: 4 Read Leveling: read_delay_fall, dq0 : 138 read_delay_rise, dq0 : 144 read_delay_fall, dq1 : 120 read_delay_rise, dq1 : 126 read_delay_fall, dq2 : 126 read_delay_rise, dq2 : 144 read_delay_fall, dq3 : 120 read_delay_rise, dq3 : 138 read_delay_fall, dq4 : 108 read_delay_rise, dq4 : 120 read_delay_fall, dq5 : 120 read_delay_rise, dq5 : 132 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 132 read_delay_fall, dq7 : 144 read_delay_rise, dq7 : 156 read_delay_fall, dq8 : 132 read_delay_rise, dq8 : 144 read_delay_fall, dq9 : 120 read_delay_rise, dq9 : 132 read_delay_fall, dq10 : 120 read_delay_rise, dq10 : 132 read_delay_fall, dq11 : 114 read_delay_rise, dq11 : 132 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 132 read_delay_fall, dq13 : 114 read_delay_rise, dq13 : 126 read_delay_fall, dq14 : 114 read_delay_rise, dq14 : 114 read_delay_fall, dq15 : 132 read_delay_rise, dq15 : 138 read_delay_fall, dq16 : 126 read_delay_rise, dq16 : 132 read_delay_fall, dq17 : 132 read_delay_rise, dq17 : 138 read_delay_fall, dq18 : 108 read_delay_rise, dq18 : 108 read_delay_fall, dq19 : 120 read_delay_rise, dq19 : 126 read_delay_fall, dq20 : 120 read_delay_rise, dq20 : 120 read_delay_fall, dq21 : 114 read_delay_rise, dq21 : 120 read_delay_fall, dq22 : 114 read_delay_rise, dq22 : 108 read_delay_fall, dq23 : 120 read_delay_rise, dq23 : 126 read_delay_fall, dq24 : 126 read_delay_rise, dq24 : 132 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 120 read_delay_fall, dq26 : 114 read_delay_rise, dq26 : 126 read_delay_fall, dq27 : 126 read_delay_rise, dq27 : 132 read_delay_fall, dq28 : 114 read_delay_rise, dq28 : 120 read_delay_fall, dq29 : 120 read_delay_rise, dq29 : 120 read_delay_fall, dq30 : 120 read_delay_rise, dq30 : 126 read_delay_fall, dq31 : 132 read_delay_rise, dq31 : 132 Write DQ Training: write_delay, dq0 : 960 write_delay, dq1 : 984 write_delay, dq2 : 968 write_delay, dq3 : 968 write_delay, dq4 : 992 write_delay, dq5 : 968 write_delay, dq6 : 968 write_delay, dq7 : 952 write_delay, dq8 : 976 write_delay, dq9 : 992 write_delay, dq10 : 992 write_delay, dq11 : 992 write_delay, dq12 : 984 write_delay, dq13 : 992 write_delay, dq14 : 992 write_delay, dq15 : 992 write_delay, dq16 : 992 write_delay, dq17 : 992 write_delay, dq18 : 1008 write_delay, dq19 : 1008 write_delay, dq20 : 992 write_delay, dq21 : 992 write_delay, dq22 : 992 write_delay, dq23 : 992 write_delay, dq24 : 976 write_delay, dq25 : 984 write_delay, dq26 : 992 write_delay, dq27 : 992 write_delay, dq28 : 992 write_delay, dq29 : 992 write_delay, dq30 : 984 write_delay, dq31 : 976 Calibration Registers: CAL_OBS_0: 0x00814654 CAL_OBS_2: 0x00814752 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00146540 CAL_OBS_5: 0x00147528 CAL_OBS_6: 0x00f4654f CAL_OBS_7: 0x03f4752f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0338 phy_grp1_slave_delay_0: 0x0338 phy_grp2_slave_delay_0: 0x034c phy_grp3_slave_delay_0: 0x034c phy_grp0_slave_delay_1: 0x034c phy_grp1_slave_delay_1: 0x0338 phy_grp2_slave_delay_1: 0x034c phy_grp3_slave_delay_1: 0x034c phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 0; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x20 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x1f DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x20 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 348 CA Bit 1 delay: 338 CA Bit 2 delay: 34c CA Bit 3 delay: 33e CA Bit 4 delay: 34e CA Bit 5 delay: 34e Write Leveling: DQ Lane 0 WRDQS: 0x0 DQ Lane 1 WRDQS: 0x0 DQ Lane 2 WRDQS: 0x0 DQ Lane 3 WRDQS: 0x0 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 109 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 160 read_delay_rise, dq0 : 160 read_delay_fall, dq1 : 160 read_delay_rise, dq1 : 160 read_delay_fall, dq2 : 160 read_delay_rise, dq2 : 160 read_delay_fall, dq3 : 160 read_delay_rise, dq3 : 160 read_delay_fall, dq4 : 160 read_delay_rise, dq4 : 160 read_delay_fall, dq5 : 160 read_delay_rise, dq5 : 160 read_delay_fall, dq6 : 160 read_delay_rise, dq6 : 160 read_delay_fall, dq7 : 160 read_delay_rise, dq7 : 160 read_delay_fall, dq8 : 160 read_delay_rise, dq8 : 160 read_delay_fall, dq9 : 160 read_delay_rise, dq9 : 160 read_delay_fall, dq10 : 160 read_delay_rise, dq10 : 160 read_delay_fall, dq11 : 160 read_delay_rise, dq11 : 160 read_delay_fall, dq12 : 160 read_delay_rise, dq12 : 160 read_delay_fall, dq13 : 160 read_delay_rise, dq13 : 160 read_delay_fall, dq14 : 160 read_delay_rise, dq14 : 160 read_delay_fall, dq15 : 160 read_delay_rise, dq15 : 160 read_delay_fall, dq16 : 160 read_delay_rise, dq16 : 160 read_delay_fall, dq17 : 160 read_delay_rise, dq17 : 160 read_delay_fall, dq18 : 160 read_delay_rise, dq18 : 160 read_delay_fall, dq19 : 160 read_delay_rise, dq19 : 160 read_delay_fall, dq20 : 160 read_delay_rise, dq20 : 160 read_delay_fall, dq21 : 160 read_delay_rise, dq21 : 160 read_delay_fall, dq22 : 160 read_delay_rise, dq22 : 160 read_delay_fall, dq23 : 160 read_delay_rise, dq23 : 160 read_delay_fall, dq24 : 160 read_delay_rise, dq24 : 160 read_delay_fall, dq25 : 160 read_delay_rise, dq25 : 160 read_delay_fall, dq26 : 160 read_delay_rise, dq26 : 160 read_delay_fall, dq27 : 160 read_delay_rise, dq27 : 160 read_delay_fall, dq28 : 160 read_delay_rise, dq28 : 160 read_delay_fall, dq29 : 160 read_delay_rise, dq29 : 160 read_delay_fall, dq30 : 160 read_delay_rise, dq30 : 160 read_delay_fall, dq31 : 160 read_delay_rise, dq31 : 160 Write DQ Training: write_delay, dq0 : 640 write_delay, dq1 : 640 write_delay, dq2 : 640 write_delay, dq3 : 640 write_delay, dq4 : 640 write_delay, dq5 : 640 write_delay, dq6 : 640 write_delay, dq7 : 640 write_delay, dq8 : 640 write_delay, dq9 : 640 write_delay, dq10 : 640 write_delay, dq11 : 640 write_delay, dq12 : 640 write_delay, dq13 : 640 write_delay, dq14 : 640 write_delay, dq15 : 640 write_delay, dq16 : 640 write_delay, dq17 : 640 write_delay, dq18 : 640 write_delay, dq19 : 640 write_delay, dq20 : 640 write_delay, dq21 : 640 write_delay, dq22 : 640 write_delay, dq23 : 640 write_delay, dq24 : 640 write_delay, dq25 : 640 write_delay, dq26 : 640 write_delay, dq27 : 640 write_delay, dq28 : 640 write_delay, dq29 : 640 write_delay, dq30 : 640 write_delay, dq31 : 640 Calibration Registers: CAL_OBS_0: 0x00814654 CAL_OBS_2: 0x00814752 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00146540 CAL_OBS_5: 0x00147528 CAL_OBS_6: 0x00f4654f CAL_OBS_7: 0x03f4752f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0338 phy_grp1_slave_delay_0: 0x0338 phy_grp2_slave_delay_0: 0x034c phy_grp3_slave_delay_0: 0x034c phy_grp0_slave_delay_1: 0x034c phy_grp1_slave_delay_1: 0x0338 phy_grp2_slave_delay_1: 0x034c phy_grp3_slave_delay_1: 0x034c phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 1; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x20 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x20 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x20 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 348 CA Bit 1 delay: 338 CA Bit 2 delay: 34c CA Bit 3 delay: 33e CA Bit 4 delay: 34c CA Bit 5 delay: 34e Write Leveling: DQ Lane 0 WRDQS: 0xa8 DQ Lane 1 WRDQS: 0xc0 DQ Lane 2 WRDQS: 0x72 DQ Lane 3 WRDQS: 0xa8 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 90 lat_adj: 3 DQS Gate Lane 1 : slave_delay: 42 lat_adj: 3 DQS Gate Lane 2 : slave_delay: 440 lat_adj: 15 DQS Gate Lane 3 : slave_delay: 464 lat_adj: 2 Read Leveling: read_delay_fall, dq0 : 138 read_delay_rise, dq0 : 144 read_delay_fall, dq1 : 120 read_delay_rise, dq1 : 126 read_delay_fall, dq2 : 126 read_delay_rise, dq2 : 144 read_delay_fall, dq3 : 120 read_delay_rise, dq3 : 138 read_delay_fall, dq4 : 108 read_delay_rise, dq4 : 120 read_delay_fall, dq5 : 120 read_delay_rise, dq5 : 132 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 132 read_delay_fall, dq7 : 144 read_delay_rise, dq7 : 144 read_delay_fall, dq8 : 138 read_delay_rise, dq8 : 144 read_delay_fall, dq9 : 120 read_delay_rise, dq9 : 132 read_delay_fall, dq10 : 120 read_delay_rise, dq10 : 126 read_delay_fall, dq11 : 114 read_delay_rise, dq11 : 126 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 126 read_delay_fall, dq13 : 120 read_delay_rise, dq13 : 126 read_delay_fall, dq14 : 114 read_delay_rise, dq14 : 114 read_delay_fall, dq15 : 132 read_delay_rise, dq15 : 132 read_delay_fall, dq16 : 126 read_delay_rise, dq16 : 132 read_delay_fall, dq17 : 132 read_delay_rise, dq17 : 138 read_delay_fall, dq18 : 108 read_delay_rise, dq18 : 108 read_delay_fall, dq19 : 120 read_delay_rise, dq19 : 126 read_delay_fall, dq20 : 120 read_delay_rise, dq20 : 120 read_delay_fall, dq21 : 114 read_delay_rise, dq21 : 120 read_delay_fall, dq22 : 114 read_delay_rise, dq22 : 108 read_delay_fall, dq23 : 120 read_delay_rise, dq23 : 126 read_delay_fall, dq24 : 126 read_delay_rise, dq24 : 132 read_delay_fall, dq25 : 120 read_delay_rise, dq25 : 120 read_delay_fall, dq26 : 114 read_delay_rise, dq26 : 126 read_delay_fall, dq27 : 126 read_delay_rise, dq27 : 132 read_delay_fall, dq28 : 114 read_delay_rise, dq28 : 114 read_delay_fall, dq29 : 120 read_delay_rise, dq29 : 120 read_delay_fall, dq30 : 120 read_delay_rise, dq30 : 126 read_delay_fall, dq31 : 132 read_delay_rise, dq31 : 132 Write DQ Training: write_delay, dq0 : 807 write_delay, dq1 : 815 write_delay, dq2 : 2047 write_delay, dq3 : 2047 write_delay, dq4 : 2047 write_delay, dq5 : 815 write_delay, dq6 : 807 write_delay, dq7 : 807 write_delay, dq8 : 2047 write_delay, dq9 : 2047 write_delay, dq10 : 2047 write_delay, dq11 : 815 write_delay, dq12 : 811 write_delay, dq13 : 815 write_delay, dq14 : 2047 write_delay, dq15 : 2047 write_delay, dq16 : 815 write_delay, dq17 : 2047 write_delay, dq18 : 2047 write_delay, dq19 : 2047 write_delay, dq20 : 815 write_delay, dq21 : 819 write_delay, dq22 : 819 write_delay, dq23 : 2047 write_delay, dq24 : 819 write_delay, dq25 : 819 write_delay, dq26 : 2047 write_delay, dq27 : 2047 write_delay, dq28 : 2047 write_delay, dq29 : 819 write_delay, dq30 : 819 write_delay, dq31 : 819 Calibration Registers: CAL_OBS_0: 0x00814654 CAL_OBS_2: 0x00814752 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00146540 CAL_OBS_5: 0x00147528 CAL_OBS_6: 0x00f4654f CAL_OBS_7: 0x03f4752f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0336 phy_grp1_slave_delay_0: 0x0336 phy_grp2_slave_delay_0: 0x034c phy_grp3_slave_delay_0: 0x034c phy_grp0_slave_delay_1: 0x034c phy_grp1_slave_delay_1: 0x0336 phy_grp2_slave_delay_1: 0x034c phy_grp3_slave_delay_1: 0x034c phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 1; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x20 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x20 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x20 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 348 CA Bit 1 delay: 338 CA Bit 2 delay: 34c CA Bit 3 delay: 33e CA Bit 4 delay: 34c CA Bit 5 delay: 34e Write Leveling: DQ Lane 0 WRDQS: 0x0 DQ Lane 1 WRDQS: 0x0 DQ Lane 2 WRDQS: 0x0 DQ Lane 3 WRDQS: 0x0 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 109 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 160 read_delay_rise, dq0 : 160 read_delay_fall, dq1 : 160 read_delay_rise, dq1 : 160 read_delay_fall, dq2 : 160 read_delay_rise, dq2 : 160 read_delay_fall, dq3 : 160 read_delay_rise, dq3 : 160 read_delay_fall, dq4 : 160 read_delay_rise, dq4 : 160 read_delay_fall, dq5 : 160 read_delay_rise, dq5 : 160 read_delay_fall, dq6 : 160 read_delay_rise, dq6 : 160 read_delay_fall, dq7 : 160 read_delay_rise, dq7 : 160 read_delay_fall, dq8 : 160 read_delay_rise, dq8 : 160 read_delay_fall, dq9 : 160 read_delay_rise, dq9 : 160 read_delay_fall, dq10 : 160 read_delay_rise, dq10 : 160 read_delay_fall, dq11 : 160 read_delay_rise, dq11 : 160 read_delay_fall, dq12 : 160 read_delay_rise, dq12 : 160 read_delay_fall, dq13 : 160 read_delay_rise, dq13 : 160 read_delay_fall, dq14 : 160 read_delay_rise, dq14 : 160 read_delay_fall, dq15 : 160 read_delay_rise, dq15 : 160 read_delay_fall, dq16 : 160 read_delay_rise, dq16 : 160 read_delay_fall, dq17 : 160 read_delay_rise, dq17 : 160 read_delay_fall, dq18 : 160 read_delay_rise, dq18 : 160 read_delay_fall, dq19 : 160 read_delay_rise, dq19 : 160 read_delay_fall, dq20 : 160 read_delay_rise, dq20 : 160 read_delay_fall, dq21 : 160 read_delay_rise, dq21 : 160 read_delay_fall, dq22 : 160 read_delay_rise, dq22 : 160 read_delay_fall, dq23 : 160 read_delay_rise, dq23 : 160 read_delay_fall, dq24 : 160 read_delay_rise, dq24 : 160 read_delay_fall, dq25 : 160 read_delay_rise, dq25 : 160 read_delay_fall, dq26 : 160 read_delay_rise, dq26 : 160 read_delay_fall, dq27 : 160 read_delay_rise, dq27 : 160 read_delay_fall, dq28 : 160 read_delay_rise, dq28 : 160 read_delay_fall, dq29 : 160 read_delay_rise, dq29 : 160 read_delay_fall, dq30 : 160 read_delay_rise, dq30 : 160 read_delay_fall, dq31 : 160 read_delay_rise, dq31 : 160 Write DQ Training: write_delay, dq0 : 640 write_delay, dq1 : 640 write_delay, dq2 : 640 write_delay, dq3 : 640 write_delay, dq4 : 640 write_delay, dq5 : 640 write_delay, dq6 : 640 write_delay, dq7 : 640 write_delay, dq8 : 640 write_delay, dq9 : 640 write_delay, dq10 : 640 write_delay, dq11 : 640 write_delay, dq12 : 640 write_delay, dq13 : 640 write_delay, dq14 : 640 write_delay, dq15 : 640 write_delay, dq16 : 640 write_delay, dq17 : 640 write_delay, dq18 : 640 write_delay, dq19 : 640 write_delay, dq20 : 640 write_delay, dq21 : 640 write_delay, dq22 : 640 write_delay, dq23 : 640 write_delay, dq24 : 640 write_delay, dq25 : 640 write_delay, dq26 : 640 write_delay, dq27 : 640 write_delay, dq28 : 640 write_delay, dq29 : 640 write_delay, dq30 : 640 write_delay, dq31 : 640 Calibration Registers: CAL_OBS_0: 0x00814654 CAL_OBS_2: 0x00814752 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00146540 CAL_OBS_5: 0x00147528 CAL_OBS_6: 0x00f4654f CAL_OBS_7: 0x03f4752f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0336 phy_grp1_slave_delay_0: 0x0336 phy_grp2_slave_delay_0: 0x034c phy_grp3_slave_delay_0: 0x034c phy_grp0_slave_delay_1: 0x034c phy_grp1_slave_delay_1: 0x0336 phy_grp2_slave_delay_1: 0x034c phy_grp3_slave_delay_1: 0x034c phy_top_train_calib_error_info: 0x00000000 DRAM VREF Values: mr12_f1_cs0: 0x00000021 mr12_f1_cs1: 0x00000027 mr12_f1_cs2: 0x00000023 mr12_f1_cs3: 0x00000027 mr12_f2_cs0: 0x00000020 mr12_f2_cs1: 0x00000027 mr12_f2_cs2: 0x00000021 mr12_f2_cs3: 0x00000027 mr14_f1_cs0: 0x00000020 mr14_f1_cs1: 0x0000000f mr14_f1_cs2: 0x0000001d mr14_f1_cs3: 0x0000000f mr14_f2_cs0: 0x0000001b mr14_f2_cs1: 0x0000000f mr14_f2_cs2: 0x0000001d mr14_f2_cs3: 0x0000000f PHY IO Pad TERM Registers: PHY_1320: 0x00014654 PHY_1321: 0x00014654 PHY_1322: 0x00014654 PHY_1323: 0x00014654 PHY_1324: 0x00014654 PHY_1325: 0x00014752 PHY_1326: 0x00014752 PHY_1327: 0x00014654 PHY_1328: 0x00014654 Enhanced Error Reporting: DQS Gate Error: 1 Training Error: 1 FSM Tran Error: 0 PLL Error: 1 Parity Error: 0 Timeout Error: 1 Timeout Error Info: dfi_rddata_valid Timeout: 1 Max PLL lock assertion Timeout: 1 Min PLL lock assertion Timeout: 0 DFI PHY master interface Timeout: 0 dfi_phyupd_req (PI - PHY) Timeout: 0 dfi_phyupd_req (CTL - PHY) Timeout: 0 dfi_lp_ack Timeout: 0 DFS change @ PI - PHY Timeout: 0 DFS change @ CTL -PHY Timeout: 0 CA / CS training Timeout: 0 WRLVL training Timeout: 0 RDGATE training Timeout: 0 RDDATA training Timeout: 0 WDQ training Timeout: 0 Training Error Info: 0x00007800 Data Slice Error Info (bits [4:0]): Byte0: 0x00000102 Byte1: 0x00000102 Byte2: 0x00000102 Byte3: 0x00000102 PLL Frequency Error: 0xf