Part Number: TDA4VM

Tool/software:

Hello,TI

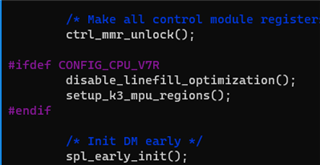

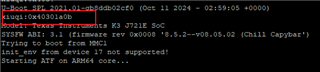

Now I research the code about SPL, found the arch\arm\mach-k3\j721e\clk-data.c can config the board clock resource.

And about program this file have some user guide to add other resources if user want to use resource early before sysfw sci load?

and for example:

CLK_MUX("mcu_clkout_mux_out0", mcu_clkout_mux_out0_parents, 2, 0x40f08010, 0, 1, 0),

how to explain this code? the param about resource name \ parents group \ the address how to get it and set?

Thanks