Tool/software:

Hi Expert,

My customer reports an issue about TPS6593 power off sequence issue,

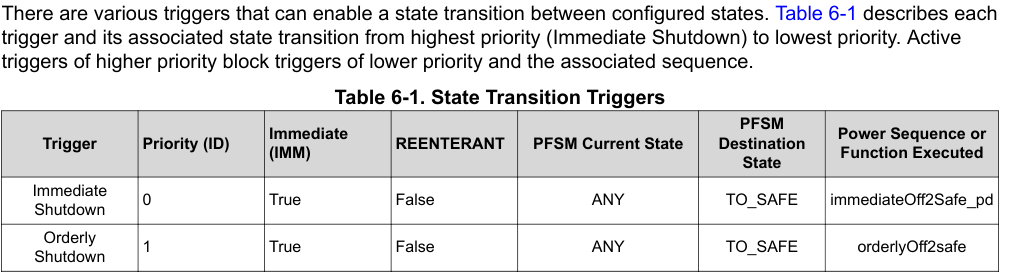

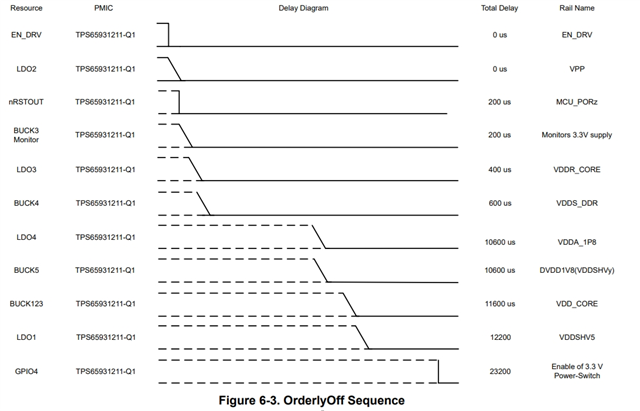

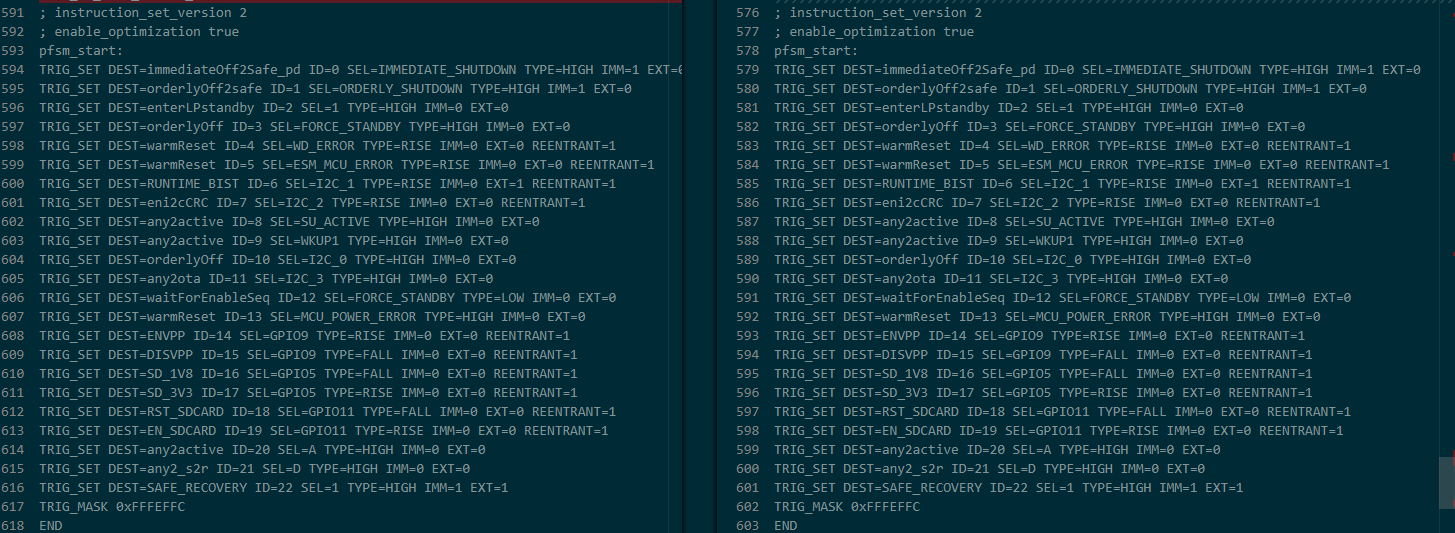

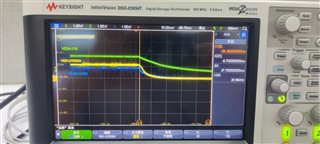

previously the NVM revison is 0x0, and the power off sequence is followed below (orderlyOff).

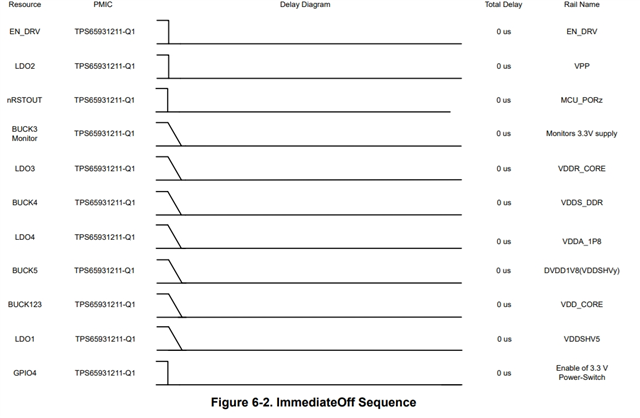

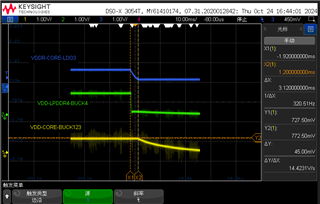

Now the new PMIC NVM revision change to 0x05. and the power off sequence change to immediateOff, power off in the same time. can you help look into this? is there any impact to AM62A?

Biao

We used the same power off method for two projects, but tested the power off timing differently. Can you help confirm if the simultaneous power off timing will have any impact on AM62A

We used the same power off method for two projects, but tested the power off timing differently. Can you help confirm if the simultaneous power off timing will have any impact on AM62A